Introduce some mathematics which we will use throughout the module.

- Syntax and Semantics—words and their meaning.

- Sets—collections of things.

- Functions—data in and answers out.

- **Syntax** refers to symbols, or notation.

- **Semantics** refers to "meaning".

- Denotation is the relation between some syntax and its semantics.

## Languages

- A **language** consists of syntax and semantics.

- The syntax consists of

- alphabet;

- rules for writing "words" from alphabet.

- In a **programming** language the "words" are *program instructions*. Rules given in the programming manual.

- The semantics of a program is what happens when the program runs.

- A set is an unordered collection of objects in which any object can appear at most once. Eg { 'a', 'g', 'r', 't' }.

- The objects in a set are called elements.

• 'a'

$$\in$$

{ 'a', 'g', 'r', 't' } and 4  $\notin$  { 'a', 'g', 'r', 't' }.

- $\mathbb{N} \stackrel{\text{def}}{=} \{0, 1, 2, ...\}$  set of **natural numbers**.

- $\blacksquare \mathbb{Z} \stackrel{\text{def}}{=} \{ \dots, -2, -1, 0, 1, 2, \dots \} \text{ set of integers.}$

The notation  $e \in A$  means "*e* is an element in *A*".

• A is a set, but its elements are not known; neither do we know what e actually is.

- *A* and *e* are **variables**—unknown *quantities*.

- When programming, you might write

n:int or int n.

to indicate that *n* is an integer, with an unknown value.

Note that

$$n \in \mathbb{Z}$$

means the same thing—and is "standard" in mathematics.

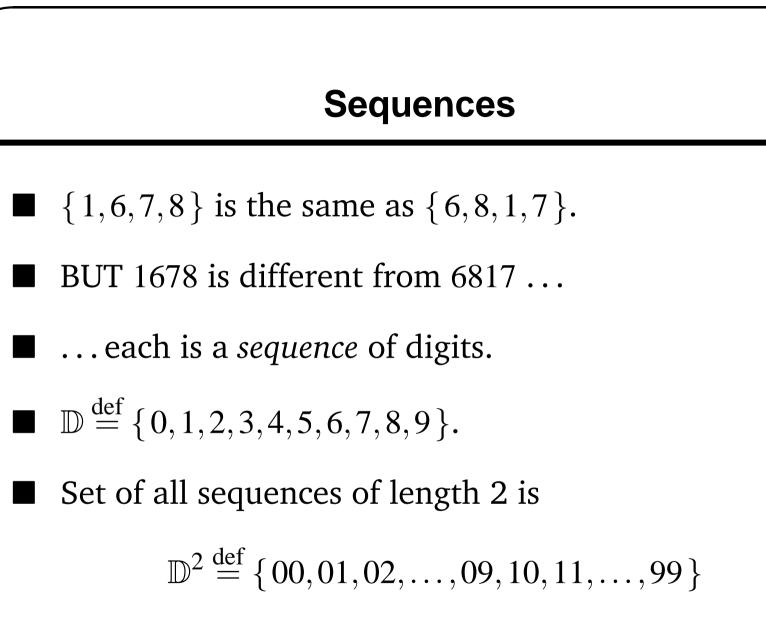

The set of all sequences of elements of *A* of length 4 is denoted by  $A^4$ .

If *A* is  $\mathbb{D}$ , then for example  $1678 \in \mathbb{D}^4$ .

If *u*, *v*, *w*, *x* are four (variable) elements of *A*, then *uvwx* denotes a single typical element of  $A^4$ , ie  $uvwx \in A^4$ .

We typically write the variables as  $a_3$ ,  $a_2$ ,  $a_1$ ,  $a_0$ , so that

$a_3a_2a_1a_0 \in A^4$

Makes "position" of each variable clear;  $a_2$  in position 2.

- $A^n$  is the set of **sequences** of elements of A of length n.

- A typical element of  $A^n$  looks like  $a_{n-1}a_{n-2}...a_0$ , where each  $a_i \in A$ .

- We refer to variable  $a_i$ , where *i* is the position 0, 1, or  $\dots n 1$ .

- We sometimes call *a<sub>i</sub>* a **component** of the sequence.

- We sometimes write  $\vec{a} = a_{n-1} \dots a_1 a_0$ .

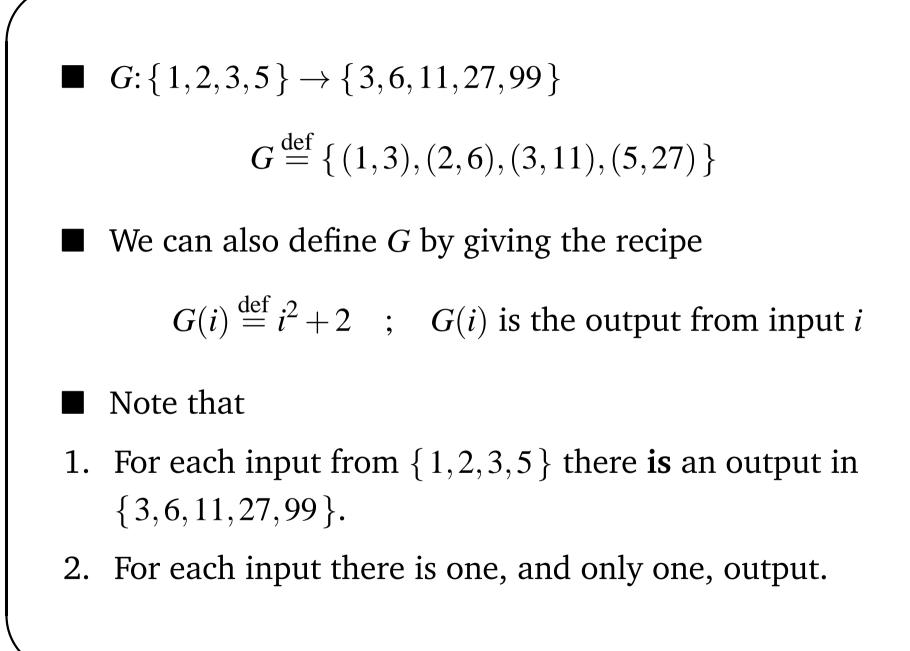

## **Functions**

■ A *function* is a machine which takes inputs and produces outputs.

- For example function *s* where  $3 \mapsto 9$  and  $-2 \mapsto 4$ .

- To *define* a function, we give

- A set of inputs (eg Z);

- a set containing all of the outputs (eg Z);

- an output (eg  $z^2$ ) for every input (eg z).

- We define a **function**  $f: A \to B$  by

- either giving a formula f(a) where a is any input from

A, with each output f(a) in B;

- or drawing arrows *a* → *b*, one for each *a* ∈ *A* (and no others), with *b* ∈ *B*;

- or writing down a set of input/output pairs (*a*, *b*),

*exactly one* pair for each *a* ∈ *A*, with *b* ∈ *B*.

- We write f(a) or f a for this unique  $b \in B$ . For example,  $G(3) = 3^2 + 2 = 11$ .

- We say *a* is the **argument** of the function.

- Also say that f(a) is the **output**, for **input** a.

Consider the following set *g* of input/output pairs { (3,8), (3,7), (9,10), (8,300) }

This is not a function { 3,8,9 } → { 4,7,8,10,300 }. Why?

Let A <sup>def</sup> = { 3,4,5 } and B <sup>def</sup> = { 4,7 } and f <sup>def</sup> = { (3,4), (4,7), (5,9) }

Then  $f: A \rightarrow B$  is not a function from A to B. Why?

B = B<sup>1</sup> = {0,1} is the set of binary numbers with 1 digit.

B<sup>2</sup> = {00,01,10,11} is the set of binary numbers with 2 digits.

- $\mathbb{B}^3 = ? \text{ is the set of binary numbers with 3 digits.}$

- $\mathbb{B}^n$  is the set of binary numbers with *n* digits.

- We shall study functions  $f: \mathbb{B}^n \to \mathbb{B}^m$  in CO1016.

- Such a function is an *n* | *m*-ary function.

- Computer circuits implement functions on binary numbers.

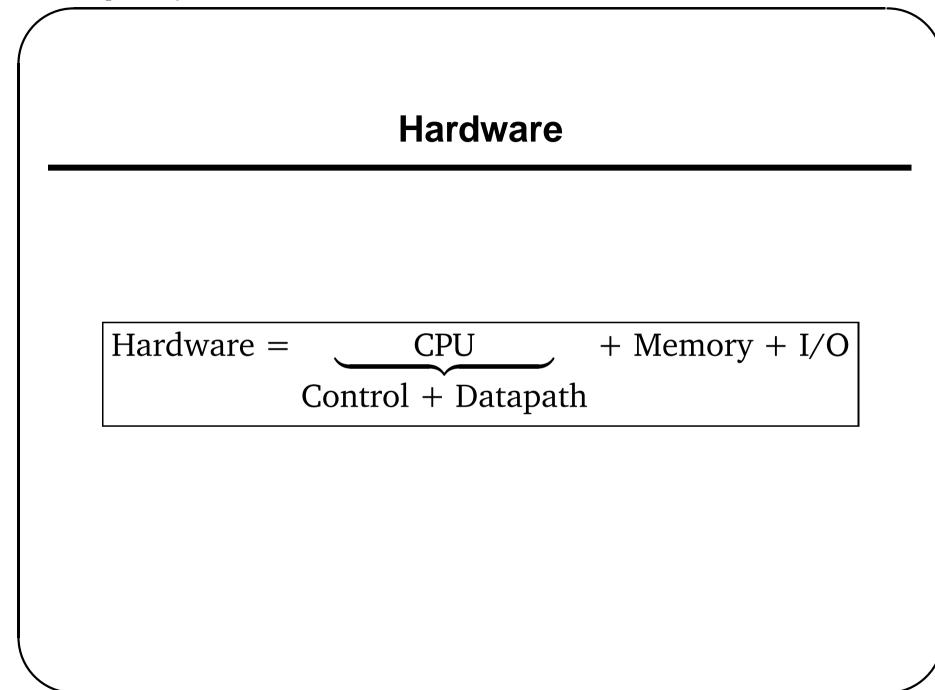

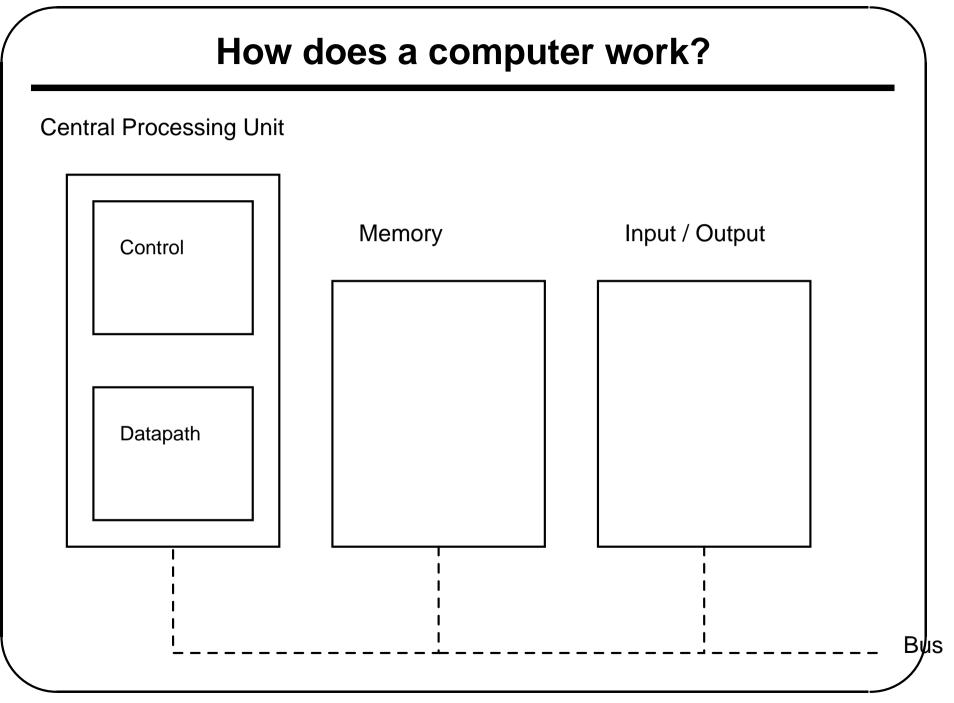

Computer = Hardware + Software

|   | а  | :=  | 0;  |        |      |    |

|---|----|-----|-----|--------|------|----|

|   | С  | :=  | 4;  |        |      |    |

| L | a  | :=  | a+c | :<br>; |      |    |

|   | С  | :=  | c-1 | L;     |      |    |

|   | if | С   | >=  | 1      | then | L; |

|   | ex | it; |     |        |      |    |

An **algorithm** is a set of instructions or "recipe".

A computer program (software) is an implementation of an algorithm.

Programs can be written in assembly language (the syntax).

• A program is a list of **assembly instructions**.

Each instruction (eg a := 0) has a semantics.

- Computers work by performing simple arithmetic. That's it!

- Graphics made from small dots of light. Position and colour of a dots changes to produce "moving" images.

- The changes are calculated using complex arithmetic—but complex calculations reduce to simple arithmetic.

A program (list of instructions) will be stored in main memory.

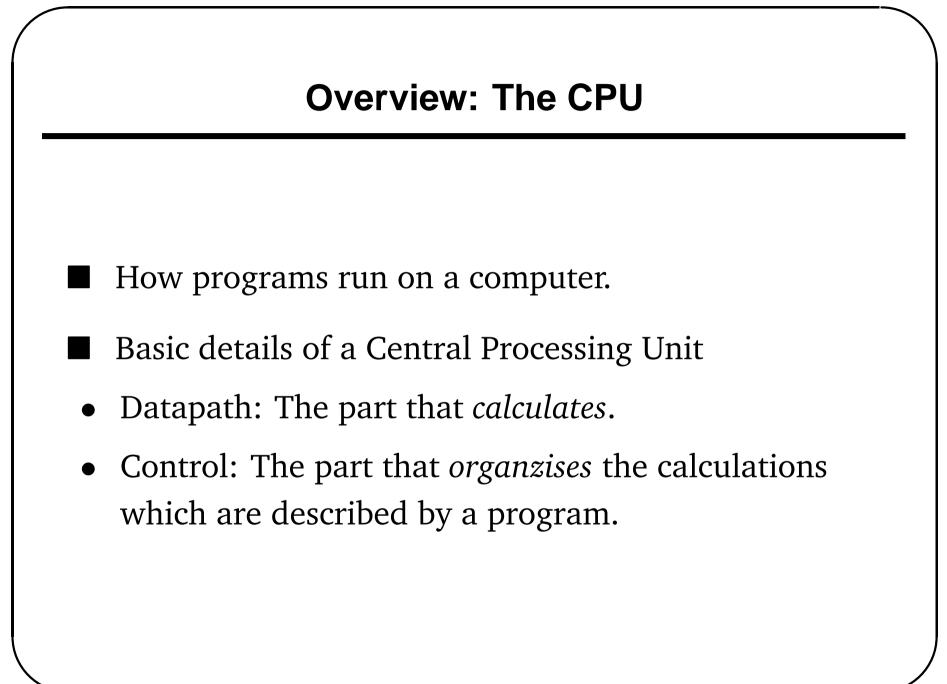

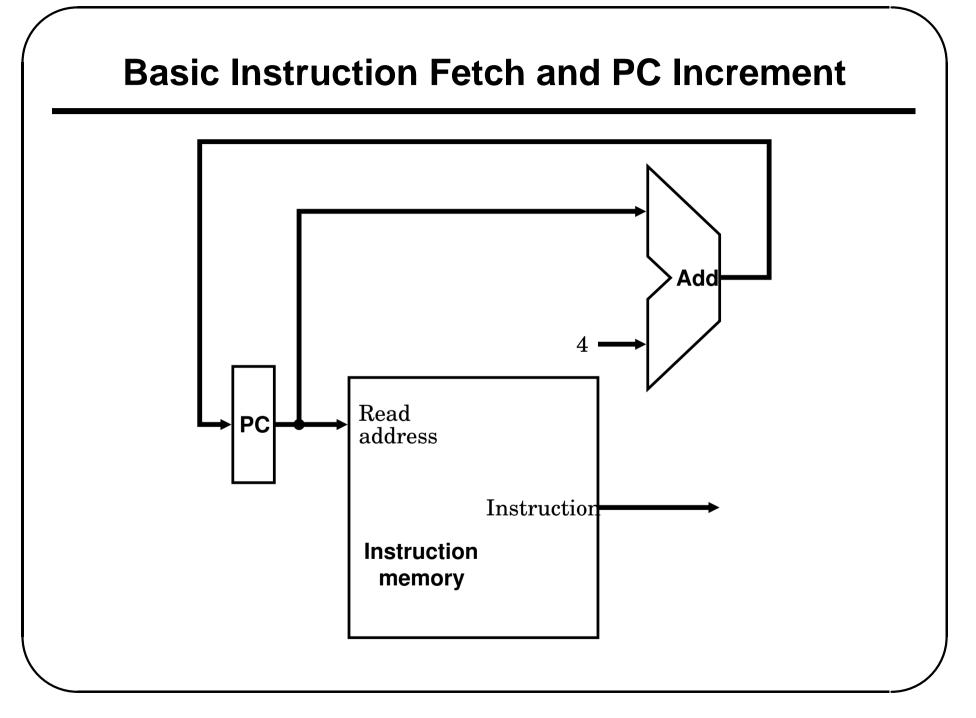

Program execution: Control copies ("fetches") each instruction into the CPU. Fetched instructions are stored in the Instruction Register (IR)

- There are many other registers. Each is computer memory; they store instructions and more besides ....

- Each instruction is executed by the **datapath**.

- The datapath is "like" a calculator ...

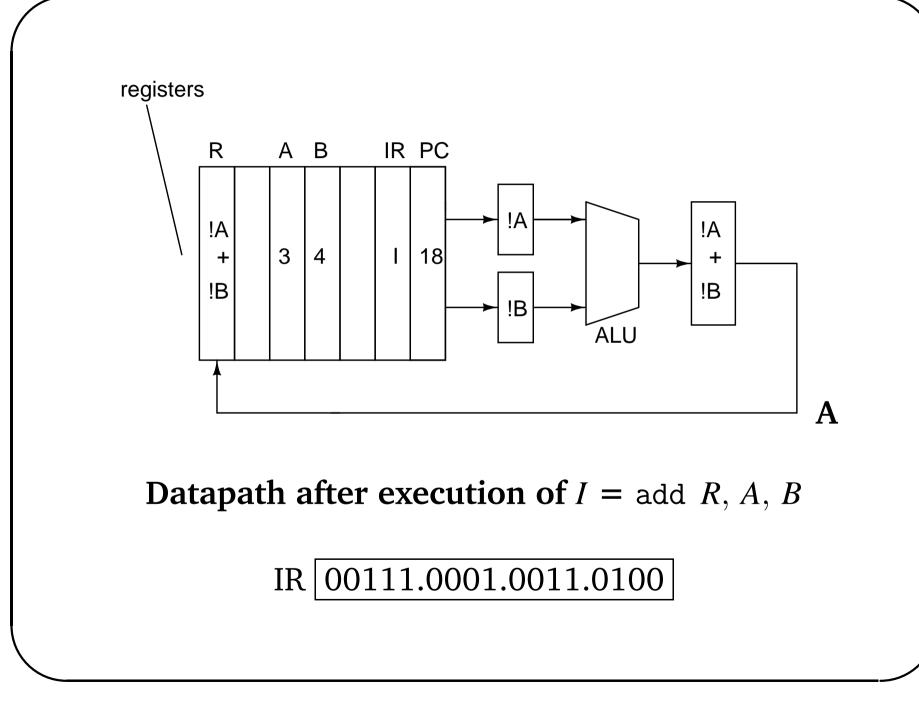

The syntax (assembly language) of our example instruction I is add R, A, B.

The *semantics* is to pass contents of A and B to the ALU, calculate the sum, then store the result in R.

Computer stores instruction as a sequence of 0s and 1s, eg 00111.0001.0011.0100. Called machine language.

Control performs a sequence of steps, called the **fetch-decode-execute (FDE)** cycle.

- **Fetch** an instruction from main memory—copy it into the IR;

- **Decode** the instruction—eg set the ALU to +;

- (**update** PC to point to next instruction;)

- **Execute** the instruction; and

- I repeat the FDE-cycle.

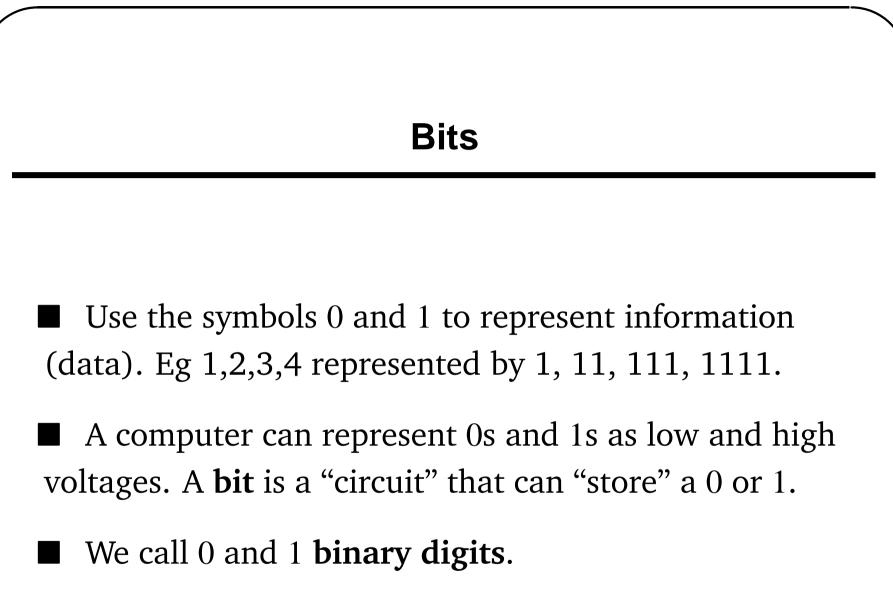

A broad understanding of how data is stored in computer memory.

- Knowledge of the different kinds of memory.

- Understanding of the technical details of how memory works.

- Know one key reason why we can build fast and cheap and big PCs.

## **Memory Characteristics**

- Memory is divided into primary memory (inboard memory) and secondary memory.

- 1. **CPU memory**, where data is stored within the CPU, either in registers or in a cache.

- 2. **Main memory**, where data is stored inside other computer circuits, known as **memory chips**.

- 3. **Outboard memory** often located on the computer, such as **magnetic discs** and so on.

- 4. Off-line memory such as magnetic tape.

- storage facilities (filing cabinets)

- locations for storing objects (draws)

- Fundamental location is a *k*-bit cell.

- addresses of locations (draw labels)

- Each cell has a numerical address.

- *contents of the locations* (documents)

A memory with *n* cells will have addresses 0 to n - 1.

- If there are *n* bits in total, we call it an *n*-bit memory.

- The cell is the smallest *individually addressable* part of a memory.

- Any *cell* is composed of *k* bits. The binary digits contained in these bits are the **contents** of the cell.

- *k*-bit cell can hold  $2^k$  different binary digit sequences. Why?

Many computers have a standard 8-bit cell called a byte location.

■ The **address of a byte location** is address of the corresponding 8-bit cell.

Groups of consecutive cells are called word

locations—used to store bigger data than will fit into a byte location.

■ The **address of a word location** is the smallest address of its cells.

■ The contents of a byte location are called a **byte**, and of a word location a **word**.

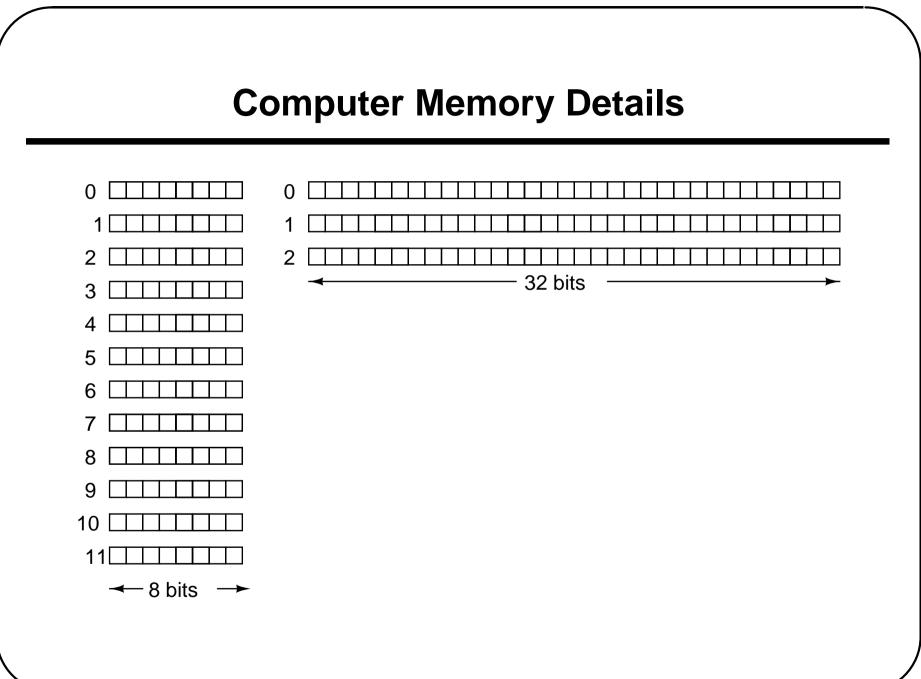

## **Organizing Memory - The Endian Systems**

- How do we arrange cells (typically byte locations) into word locations? Why is the arrangement important?

- Cells in any word location can be addressed from "left to right", or "right to left".

- The left to right numbering is called **big endian**, and the right to left **little endian**.

Integers are stored in word locations—they can be big! Store  $2^{31}$  as  $1\vec{0}^{bin} = 1000...000^{bin}$ —a 32-bit word.

- 7 will also be stored in a word location, as  $\vec{0}111^{bin}$ .

- The 1s will appear in byte locations 3 or 7 or 11 or 15 in the big endian system.

- 'A' to 'Z' will be represented by small integers, known as **character codes**. Eg **ASCII**—'A' is stored as the binary for 65.

- Thus codes are stored in cells (byte locations)—check this!

- Problems can arise when data is transferred from a big endian (SPARC) to a little endian (Intel) computer ...

## **Physical Types of Primary Memory**

Please read pages 20 to 22 which describe **Random Access Memory (RAM), Static** RAM (**SRAM**) etc etc

# **Cache Memory**

- Can use hierarchy to build a modern computer:

- fast

- large capacity memory

- good price

- This is achieved (in part) by using a **cache** ...

- Given any instruction, it is likely that the next few instructions to be executed are nearby (*local*) in memory.

- This is called the **locality principle**.

- Such a small group of instructions is called a **cluster**.

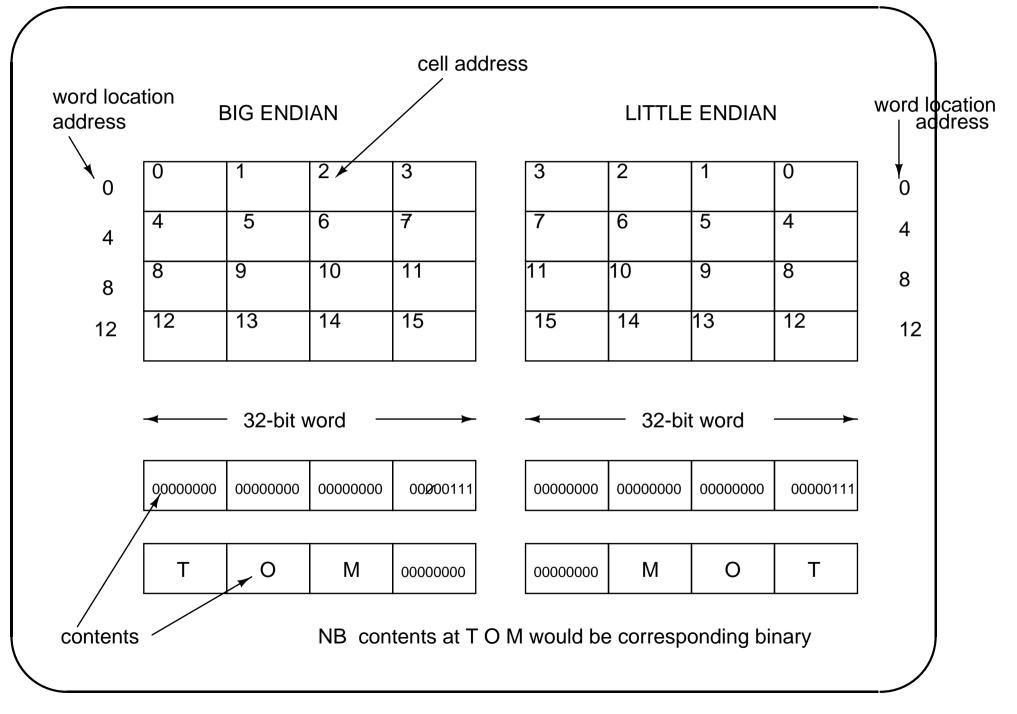

■ **Cache** is fast memory found near, or on, the CPU. It consists of **lines**.

Each line stores (clusters of) instructions.

■ Fetch cycle: control will check if the next instruction is in a cache line. If so, it will be fetched from cache to CPU.

■ If not, control will fetch the next instruction's cluster from main memory into the cache, and place the next instruction into the CPU.

• We formalise the idea of a cluster as a **block**.

CO1016 Computer Systems 2011/12

If instruction *I* is held in the cell with address *a*, then

- *I* appears in block *a DIV K*;

- block *b* is copied into cache line *b* MOD C; and

- the first cell in block *b* has address b \* K.

## **Secondary Memory**

Secondary Memory Read Chapter 5 of Stallings.

Additional information can be found on pages 69 to 88 of Tannenbaum. Non examinable.

- Decimal Number Systems (10 fingers)

- Binary Numbers in Computers (2 fingers)

- Binary Addition (adding with 2 fingers)

- 2s-Complement Numbers (dealing with negatives)

- Logical Operations (true and false)

How to represent integers in a computer as binary numbers.

■ Learn about other representations.

•

$$\mathbb{N} \stackrel{\text{def}}{=} \{0, 1, 2, ...\} \text{ and } \mathbb{Z} \stackrel{\text{def}}{=} \{..., -1, 0, 1, ...\}.$$

Recall Roman representation.

- A **representation** of  $\mathbb{N}$  is given by

- a set of symbols *S*

- a (bijective) function  $\llbracket \rrbracket: S \to \mathbb{N}$

- A symbol *s* **denotes** the number  $[s] \in \mathbb{N}$ .

# **Binary numbers**

- *binary numbers* are a representation for integers.

- The **binary digits** are 0 or 1.

- A binary number is a sequence of binary digits, an element of  $\mathbb{B}^k$ , eg 10010<sup>bin</sup>  $\in \mathbb{B}^5$ .

- We often use d or  $d_i$  to stand for a binary digit.

- Write a *k*-digit binary number as

$$d_{k-1}\ldots d_0^{bin}\in \mathbb{B}^k$$

$$d_{k-1} \dots d_0^{bin}$$

is a sequence of digits.

It denotes an integer

$$\llbracket d_{k-1} \dots d_0^{bin} \rrbracket$$

.

$$\begin{bmatrix} 10^{bin} \end{bmatrix} = 1 * 2^{1} + 0 * 2^{0} = 2^{1} + 0 = 2 + 0 = 2$$

$$\begin{bmatrix} 10100^{bin} \end{bmatrix} = 2^{4} + 0 + 2^{2} + 0 + 0 = 16 + 0 + 2 + 0 + 0 = 20$$

A digit  $d_i$ , 0 or 1, tells us how many  $2^i$  we have, zero or one! In general

$$\llbracket d_{k-1}d_{k-2}\dots d_0^{bin} \rrbracket = d_{k-1} * 2^{k-1} + d_{k-2} * 2^{k-2} + \dots + d_0 * 2^0$$

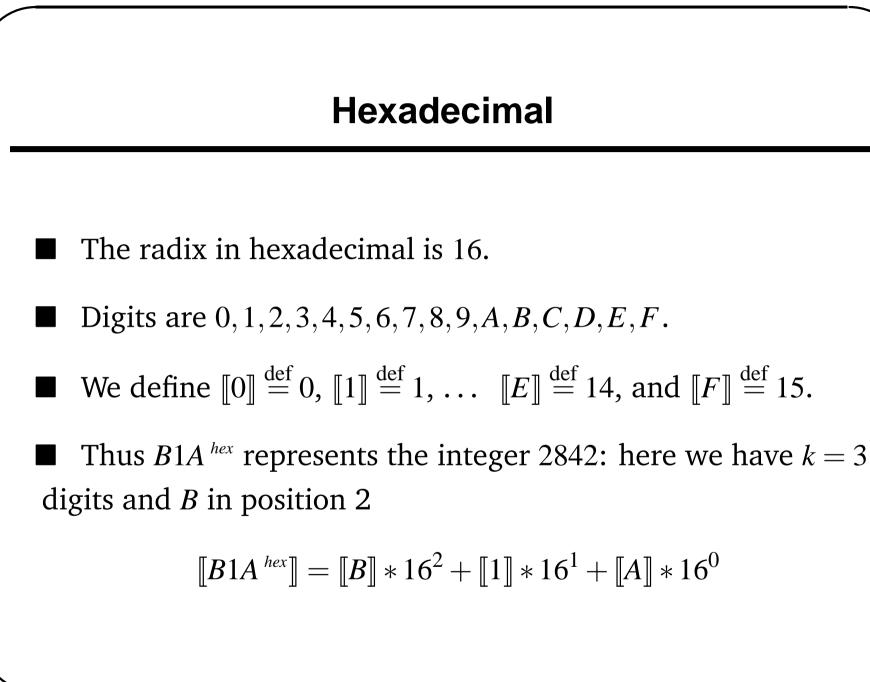

# Radix (Base)

- 10 and 2 are referred to as a **radix** or **base**.

- To represent a number in radix r, we take r different symbols. Each symbol is called a **digit**.

- Each digit denotes a number; we write  $\llbracket d \rrbracket$  for the integer denoted by the digit *d*.

- A number is represented with radix *r* as  $d_{k-1} \dots d_0^r$ , where

$$\llbracket d_{k-1} \dots d_0 r \rrbracket \stackrel{\text{def}}{=} \llbracket d_{k-1} \rrbracket * r^{k-1} + \llbracket d_{k-2} \rrbracket * r^{k-2} + \dots + \llbracket d_0 \rrbracket * r^0$$

- Store a binary number using bits.

- Must represent numbers within a finite range.

- In 4 bits, the largest number is given by 1111<sup>*bin*</sup>, that is

$$2^3 + 2^2 + 2^1 + 2^0 = 15 = 2^4 - 1$$

- If k bits represent a number n, then  $0 \le n \le 2^k 1$ .

- We shall say the computer has *k*-bit numbers or equivalently *k*-digit numbers.

- Write a *k*-bit/digit number as  $d_{k-1} \dots d_0^{bin}$  or  $\vec{d}$ .

- We call  $d_{k-1}$  the **most significant** digit, and  $d_0$  the **least significant**.

- If we have  $k \stackrel{\text{def}}{=} 6$  bits, then the number 3 is represented by 000011 <sup>*bin*</sup>.

• We call 0 and 1 **complements** of each other, and write  $\overline{0} \stackrel{\text{def}}{=} 1$  and  $\overline{1} \stackrel{\text{def}}{=} 0$ .

If  $\vec{d}^{bin} = d_{k-1} \dots d_0^{bin}$  is a binary number, then its **digitwise complement** is defined to be  $\overline{d_{k-1}} \dots \overline{d_0}^{bin}$ .

• We will sometimes denote the digitwise complement of  $\vec{d}^{bin}$  by  $\overline{\vec{d}^{bin}}$  or just simply  $\vec{d}$ .

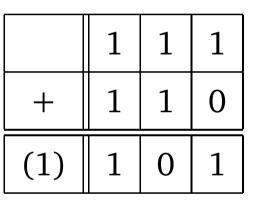

# **Binary Addition**

- In a + b, a and b are **operands** and + the **operator**.

- Recall digitwise addition. If  $d_2d_1d_0^{dec} = 927^{dec}$  and  $d'_2d'_1d'_0^{dec} = 436^{dec}$ , then the sum is

- $s_3 = (0+0+1) MOD 10 = 1$   $s_2 = (9+4+0) MOD 10 = 3$   $s_1 = (2+3+1) MOD 10 = 6$  $s_0 = (7+6+0) MOD 10 = 3$

We describe formally the **digitwize algorithm** to compute  $\vec{s}^{dec} \stackrel{\text{def}}{=} \vec{d}^{dec} + \vec{d'}^{dec}$ .  $\blacksquare \quad carry_0 \stackrel{\text{def}}{=} 0.$ If  $i \ge 0$  then  $s_i \stackrel{\text{def}}{=} (d_i + d'_i + carry_i) MOD$  10 and  $carry_{i+1} \stackrel{\text{def}}{=} (d_i + d'_i + carry_i) DIV 10$ To add binary numbers, change 10 to 2.

Check that  $10^{bin} + 111^{bin} = 1001^{bin}$  by showing that the algorithm gives rise to the following table

| $\vec{d}^{bin}$      |   |   | 1 | 0 |

|----------------------|---|---|---|---|

| $\vec{d'}^{bin}$     |   | 1 | 1 | 1 |

| carry <sup>bin</sup> | 1 | 1 | 0 | 0 |

| $\vec{S}^{bin}$      | 1 | 0 | 0 | 1 |

#### Correctness

Let

$$z = \llbracket \vec{d}^{bin} \rrbracket$$

, and  $z' = \llbracket \vec{d'}^{bin} \rrbracket$ .

- Digitwise algorithm calculates  $\vec{s}^{bin}$  from  $\vec{d}^{bin}$  and  $\vec{d'}^{bin}$ .

- The algorithm is **correct** if  $[\![\vec{s}^{bin}]\!] = z + z'$ .

- We say z + z' is **correctly** represented by  $\vec{s}^{dec}$ .

- I Thus a formal statement of correctness is

$$[\vec{s}^{\textit{bin}}]] = [\![\vec{d}^{\textit{bin}}]\!] + [\![\vec{d'}^{\textit{bin}}]\!]$$

where = is **test for equality** (written == in Java).

- How to represent any integer in a computer.

- How to add and subtract in a computer.

- Is the computer correct?

### **2s-Complement Numbers**

- Must represent all *integers* in a computer.

- In a k + 1-bit 2s-complement system, the bit in position k will be 0 for positive integers and zero, and 1 otherwise.

- Given a 2s-complement number  $d_k \dots d_0^{bin}$ , the actual integer it represents is, by definition,

$$( [d_k \dots d_0^{bin}]) \stackrel{\text{def}}{=} -d_k * 2^k + [ [d_{k-1} \dots d_0^{bin}] ] = -d_k * 2^k + (d_{k-1} * 2^{k-1} + d_{k-2} * 2^{k-2} + \dots + d_0 * 2^0)$$

If k = 5, then  $(000111^{bin}) = -0 * 2^5 + 7 = 7$ but  $(100111^{bin}) = -1 * 2^5 + 7 = -32 + 7 = -25$

Note also that

$25 = (011001^{bin}).$

- If *m* is any integer, its **negation** is defined to be -1 \* m.

- Subtraction performed by adding the negation of an integer.

- The negation of the integer represented by  $\vec{b}^{bin}$ , is represented by the k + 1 2s-complement number number  $\vec{b}^{bin} + 1^{bin}$ .

- Any integer *z*, to be representable with k + 1 bits, must lie in the range below

$$-2^k \le z \le 2^k - 1$$

■ We look at what happens when numbers get too big for a computer.

■ We see that sometimes we can get unexpected, correct results.

Recall correctness:

$$\llbracket \vec{s}^{bin} \rrbracket = \llbracket \vec{b}^{bin} \rrbracket + \llbracket \vec{b'}^{bin} \rrbracket \qquad (EQ?)$$

■ Idea: Given  $\vec{b}^{bin}$  and  $\vec{b'}^{bin}$ , compute  $\vec{s}^{bin}$  using the Digitwise Alg. THEN check if EQ? is true or false.

■ If true, algorithm (or computer) is correct.

| $ec{b}^{bin}$   |   | 0 | 1 | 1 |

|-----------------|---|---|---|---|

| $ec{b'}^{bin}$  | + | 1 | 0 | 0 |

| $\vec{S}^{bin}$ | 0 | 1 | 1 | 1 |

On paper:  $[0111^{bin}] = 7 = 3 + 4 = [011^{bin}] + [100^{bin}].$

**3**-bits only:  $[111^{bin}] = 7 = 3 + 4 = [011^{bin}] + [100^{bin}].$

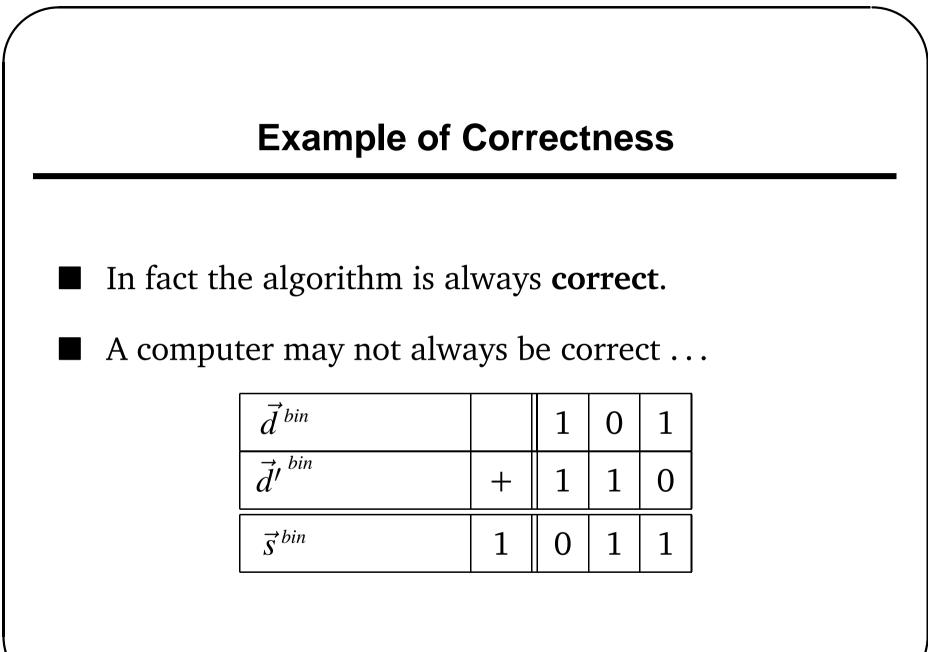

| $ec{b}^{bin}$    |   | 1 | 0 | 1 |

|------------------|---|---|---|---|

| $\vec{b'}^{bin}$ | + | 1 | 1 | 0 |

| $\vec{S}^{bin}$  | 1 | 0 | 1 | 1 |

On paper:

$$[1011^{bin}] = 11 = 5 + 6 = [101^{bin}] + [110^{bin}]$$

3 bits:

$$[011^{bin}] = 3 \neq 5 + 6 = [101^{bin}] + [110^{bin}]$$

A 3-bit computer would give incorrect answer

In fact the following conditions are *equivalent* ways of expressing *k*-bit correctness

$$[[s_{k-1} \dots s_0^{bin}]] = [[b_{k-1} \dots b_0^{bin}]] + [[b'_{k-1} \dots b'_0^{bin}]]$$

$$0 \le [[b_{k-1} \dots b_0^{bin}]] + [[b'_{k-1} \dots b'_0^{bin}]] \le 2^k - 1$$

both true or both false.

#### **2s-Complement Numbers**

Let k = 2, with 3 bits for 2s-complement numbers. There may be a carry of 1, but with the *computer sum (result)* correct!!!

Here the computer sum is 101 with k + 1 = 3 digits/bits. The carry in *position* k + 1 = 3 is (1).

$$(101) = -3 = (111) + (110)$$

#### Sign-bit Conditions

- Let *P* be "the sign bits of the two operands are complementary  $(b_k = \overline{b'_k})$ ";

- and let Q be "the sign bits of the two operands are identical, and also the same as the sign bit of the computer sum (b<sub>k</sub> = b'<sub>k</sub> = s<sub>k</sub>)".

If |P or Q| is true, then the computer sum will be correct.

Result = Computer Sum = k + 1-digit answer (excluding any carry into *position* k + 1—see previous slide). The following conditions are *equivalent* for 2s-complement correctness.

•

$$(s_k \dots s_0^{bin}) = (b_k \dots b_0^{bin}) + (b'_k \dots b'_0^{bin})$$

•

$$-2^k \le (b_k \dots b_0^{bin}) + (b'_k \dots b'_0^{bin}) \le 2^k - 1$$

• *P* or *Q* is true.

■ We learn about simple logic, and some related functions.

We shall see how these functions might be used by a computer.

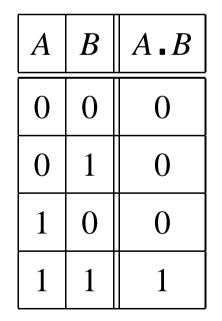

# AND and OR

- I Typically use 1 to denote truth, and 0 to denote falsity.

- We shall soon use the logic functions  $: \mathbb{B}^2 \to \mathbb{B}$  and  $+_{or}: \mathbb{B}^2 \to \mathbb{B}$ . Refer to these as **AND** and **OR**.

- We will sometimes write sequences  $d_k \dots d_0$  using brackets:  $(d_k, \dots, d_0)$ . Call  $(d_1, d_0)$  a **pair** and  $(d_2, d_1, d_0)$  a **triple**.

AND input pair (d, d') is mapped to an output written in infix notation  $d \cdot d'$ .

■  $d \cdot d'$  is 1 precisely when both d and d' are 1, and otherwise  $d \cdot d'$  is 0.

• OR input pair (d, d') is mapped to an output written in infix notation  $d +_{or} d'$ .

■  $d +_{or} d'$  is 1 precisely when at least one of d or d' are 1, and otherwise  $d +_{or} d'$  is 0.

### **Truth Tables**

We give the functions  $\cdot$  and  $+_{or}$  by explicitly listing inputs and outputs in tables; in work on digital circuits we often use *A*, *B* and *C* to stand for binary digits 0 or 1. The tables give  $(A,B) \mapsto A +_{or} B$  where  $+_{or}: \mathbb{B}^2 \to \mathbb{B}$ , and similarly  $\cdot$ .

| A | B | $A +_{or} B$ |  |

|---|---|--------------|--|

| 0 | 0 | 0            |  |

| 0 | 1 | 1            |  |

| 1 | 0 | 1            |  |

| 1 | 1 | 1            |  |

### **Zero Extension**

- Sometimes, a binary number will be stored in *k* bits.

- We will then want to move the number into k' + k bits, so that *its denotation is not changed*.

- We fill the extra bits with k' zeros. This is called a **zero** extension.

- We can model it as a function

$$\mathbb{B}^k \longrightarrow \mathbb{B}^{k'+k} \qquad \vec{b} \mapsto \vec{0}\vec{b}$$

where  $\vec{0}$  denotes k' zeros.

We will sometimes write the output as  $zx(\vec{b})$ .

To move a k + 1 bit 2s-complement number  $\delta \vec{b}$  into k' + k + 1 bits copy the sign bit into the new k' positions. This is called a **sign extension**.

We can model it as a function

$$\mathbb{B}^{k+1} \longrightarrow \mathbb{B}^{k'+k+1} \qquad \delta \vec{b} \mapsto \vec{\delta} \delta \vec{b}$$

where  $\vec{\delta}$  means a sequence of  $k' \delta s$ .

• We will sometimes write the output as  $sx(\delta \vec{b})$ .

## **Overview: Switching Algebras and Basic Circuits**

■ We describe the *Switching Algebra* which gives a mathematical model of simple circuits.

Then we show how to use such models to design and implement digital circuits.

The **switching algebra** consists of the following five things:  $(\mathbb{B}, \cdot, +_{or}, -, 0, 1).$

The functions satisfy certain properties.

| Property    | $+_{or}$                                        |  |  |

|-------------|-------------------------------------------------|--|--|

| Idempotent  | $A +_{or} A = A$                                |  |  |

| Complement  | $A +_{or} \overline{A} = 1$                     |  |  |

| Associative | $A +_{or} (B +_{or} C) = (A +_{or} B) +_{or} C$ |  |  |

$\blacksquare \overline{A} \cdot B +_{or} C \text{ stands for } ((\overline{A}) \cdot B) +_{or} C.$

## **Implementing Functions by Circuits**

- We implement  $n \mid m$ -ary functions over  $\mathbb{B}$  as digital circuits. For example,  $f: \mathbb{B}^3 \to \mathbb{B}^4$  and  $(1,0,1) \mapsto (1,1,0,0)$ ,

- We shall represent such circuits with pictures.

- The horizontal input lines denote wires with a voltage.

- Each voltage indicates a binary digit, which will be one of the function's input components.

We sometimes *label* input and output lines, eg by A.

■ We talk about the "input line" *A* to mean the physical wire into the circuit.

- The line *A* carries or holds a binary digit value.

- A gate is defined to be an electrical circuit which computes certain simple functions over  $\mathbb{B}$ .

An **AND** gate computes ... ; there are other gates ...

There are also  $m \mid 1$ -ary versions of  $\cdot$  and  $+_{or}$ . If m = 3 then  $\cdot: \mathbb{B}^3 \to \mathbb{B}$  and we write  $A \cdot B \cdot C$  for the output to input (A, B, C). The output  $A \cdot B \cdot C = 1$  only when A = 1 and B = 1 and C = 1.

| A | B | С | <i>A</i> <b>.</b> <i>B</i> <b>.</b> <i>C</i> |

|---|---|---|----------------------------------------------|

| 0 | 0 | 0 | 0                                            |

| 0 | 0 | 1 | 0                                            |

| 0 | 1 | 0 | 0                                            |

|   | - | • |                                              |

| 1 | 1 | 0 | 0 |

|---|---|---|---|

| 1 | 1 | 1 | 1 |

We want to show how to build (implement) a circuit for an  $n \mid m$ -ary function.

Each such function is equivalent to m different  $n \mid 1$ -ary functions . . . see pictures from the lecture.

- Thus we just demonstrate by example how to implement  $n \mid 1$ -ary functions.

- We start from a truth table ...

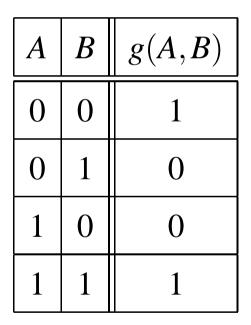

We look at an example of a 2 | 1-ary function:

We construct a **Sum-of-Products** expression ...

| A | B | C | $f_0(A,B,C)$ |

|---|---|---|--------------|

| 0 | 0 | 0 | 1            |

| 0 | 1 | 0 | 0            |

| 0 | 0 | 1 | 1            |

| 0 | 1 | 1 | 1            |

| 1 | 0 | 0 | 0            |

| 1 | 1 | 0 | 0            |

| 1 | 0 | 1 | 0            |

| 1 | 1 | 1 | 1            |

#### We have

$$g(A,B) = \overline{A} \cdot \overline{B} +_{or} A \cdot B$$

$$f_0(A,B,C) = \overline{A} \cdot \overline{B} \cdot \overline{C} +_{or} \overline{A} \cdot \overline{B} \cdot C +_{or} \overline{A} \cdot B \cdot C +_{or} \overline{A} \cdot B \cdot C +_{or} A \cdot B \cdot C$$

It is easy to make a circuit to implement any  $n \mid 1$ -ary function given by a Sum-of-Products expression. See the notes and lectures.

Circuits may not be optimal:

$$\overline{A} \cdot \overline{B} \cdot \overline{C} +_{or} \overline{A} \cdot \overline{B} \cdot C +_{or} \overline{A} \cdot B \cdot C +_{or} A \cdot B \cdot C$$

$$= \overline{A} \cdot \overline{B} \cdot (\overline{C} +_{or} C) +_{or} (\overline{A} +_{or} A) \cdot B \cdot C$$

$$= \overline{A} \cdot \overline{B} \cdot 1 +_{or} 1 \cdot B \cdot C$$

$$= \overline{A} \cdot \overline{B} +_{or} B \cdot C$$

## **Multiplexor**

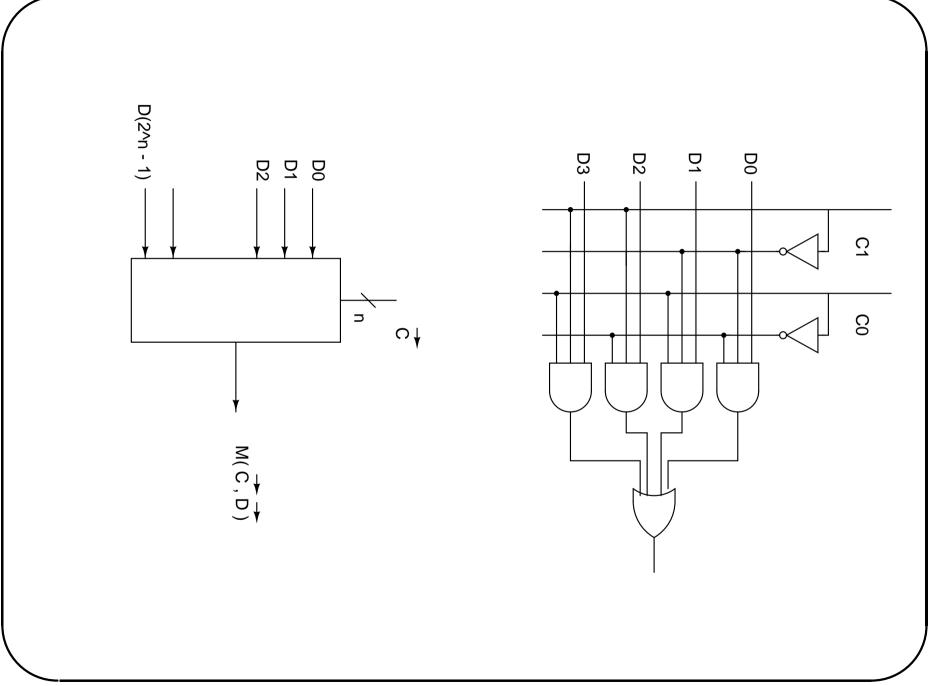

A multiplexor has  $n + 2^n$  input lines which divide up into *n* control input lines and  $2^n$  data input lines.

Truth table when *n* is 3 ( $d_i \in \mathbb{B}$ )

| $C_2$ | $C_1$ | $C_0$ | $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ | M     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1     | 0     | 1     | $d_7$ | $d_6$ | $d_5$ | $d_4$ | $d_3$ | $d_2$ | $d_1$ | $d_0$ | $d_5$ |

■ Value of output is  $D_{\llbracket C_2 C_1 C_0 \rrbracket}$ . Thus we write  $M(\vec{C}, \vec{D}) = D_{\llbracket C_2 C_1 C_0 \rrbracket}$ .

• A **decoder** has n input lines and  $2^n$  output lines.

For each of the  $2^n$  input tuples, one of the output lines is set to 1 and the others are set to 0.

- Usually output line  $L_{\|\vec{b}\|} = 1$  where  $\vec{b}$  is the input tuple.

- Use a decoder to enable/disable one of many circuits.

In many digital circuits, the timing of various processes and tasks is crucial.

- A **pulse** is a voltage of 1 which lasts for a short time.

- A **clock** is a circuit which generates a series of pulses.

Each pulse lasts for fixed time, and there is a fixed interval between pulses during which the voltage produced is 0.

- The production of such a high and low voltage is called a **clock cycle**.

- The total time taken for this is called the clock cycle time or period.

- The start time of a clock pulse is called a **rising edge**; the **falling edge** is when the pulse ends.

# Adders

- We want a circuit (**full adder**) to perform addition of single binary digits.

- It will have three input lines for  $carry_i$ , and  $d_i$  and  $d'_i$ .

- It will have two output lines for  $s_i$  and  $carry_{i+1}$ .

| a | b | CarryIn | CarryOut | Sum |

|---|---|---------|----------|-----|

| 0 | 0 | 0       | 0        | 0   |

| 0 | 1 | 0       | 0        | 1   |

| 0 | 1 | 1       | 1        | 0   |

| 1 | 1 | 0       | 1        | 0   |

| 1 | 1 | 1       | 1        | 1   |

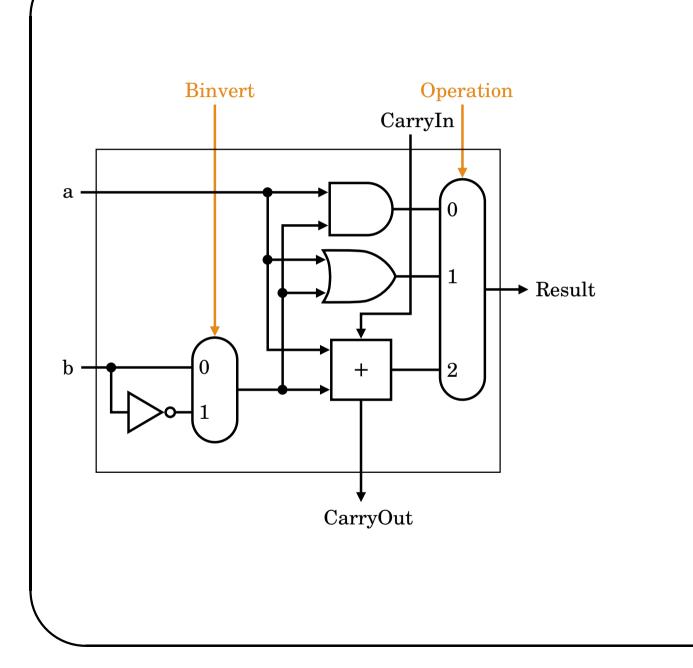

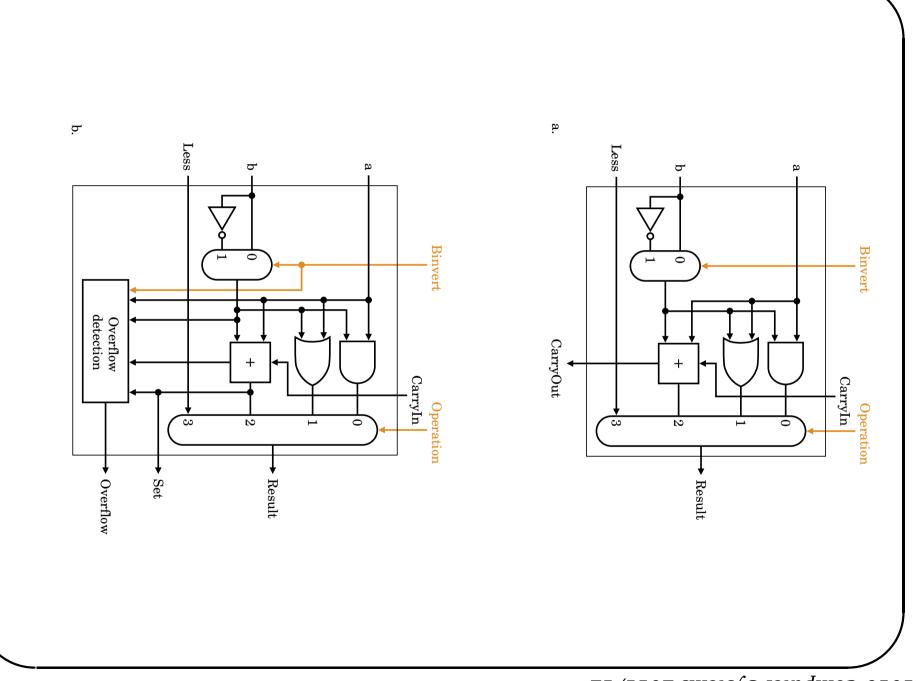

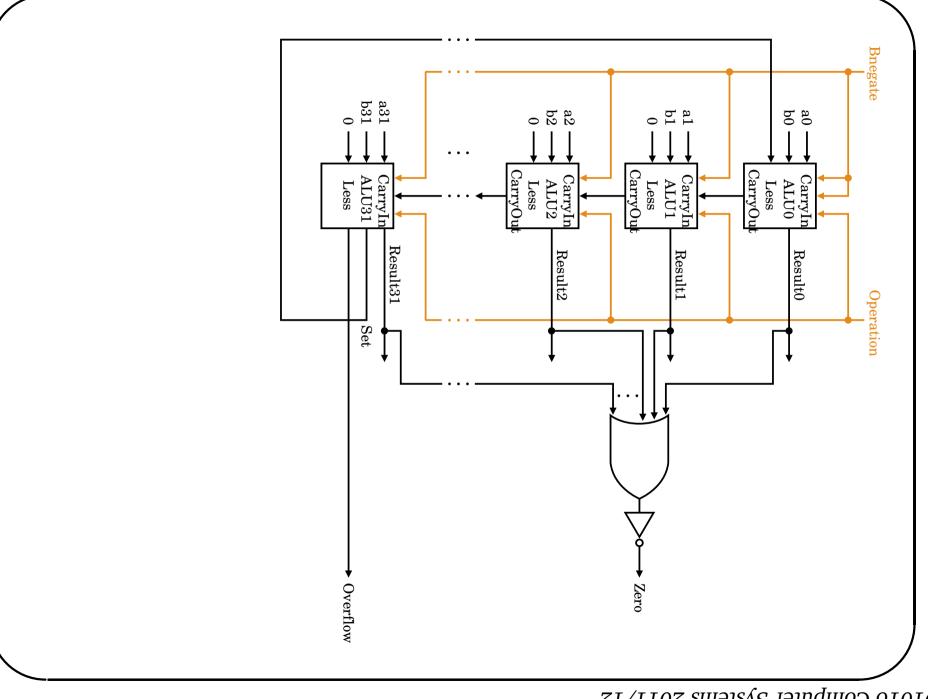

### **Arithmetic Logical Units**

Two *Data Input k-bit busses* (each holding a *k*-digit binary number  $\vec{a}$  and  $\vec{b}$ ).

One Output k-bit bus value (holds result  $\vec{r}$ , given by a selected function applied to the two k-bit integers).

One Control Input bus which will be used to select the ALU function. KEY IDEA.

• We shall design an ALU where k = 32, with functions from Chapter 3, and ...

the "set on less than" slt function which returns

$$r_{31} = 0, \dots, r_1 = 0, r_0 = 1$$

if  $(|\vec{a}|^{bin}) < (|\vec{b}|^{bin})$

$r_{31} = 0, \dots, r_1 = 0, r_0 = 0$  if otherwise

A single bit output line Zero which returns 1 when any result is  $\vec{0}$ , and 0 otherwise.

■ A single bit output line which will hold 1 when a function causes overflow, and will hold 0 otherwise.

- Sequential circuits may have different "ouputs" for the same "input".

- (They implement *relations*.)

- I These circuits can be used to build digital memory.

- Combinational circuits are functions.

- A sequential circuit can have many allowed outputs for a given input.

- Such circuits implement not functions, but *relations*.

- For such "allowed" input and output, the circuit is **stable**.

- Otherwise the circuit is **unstable**.

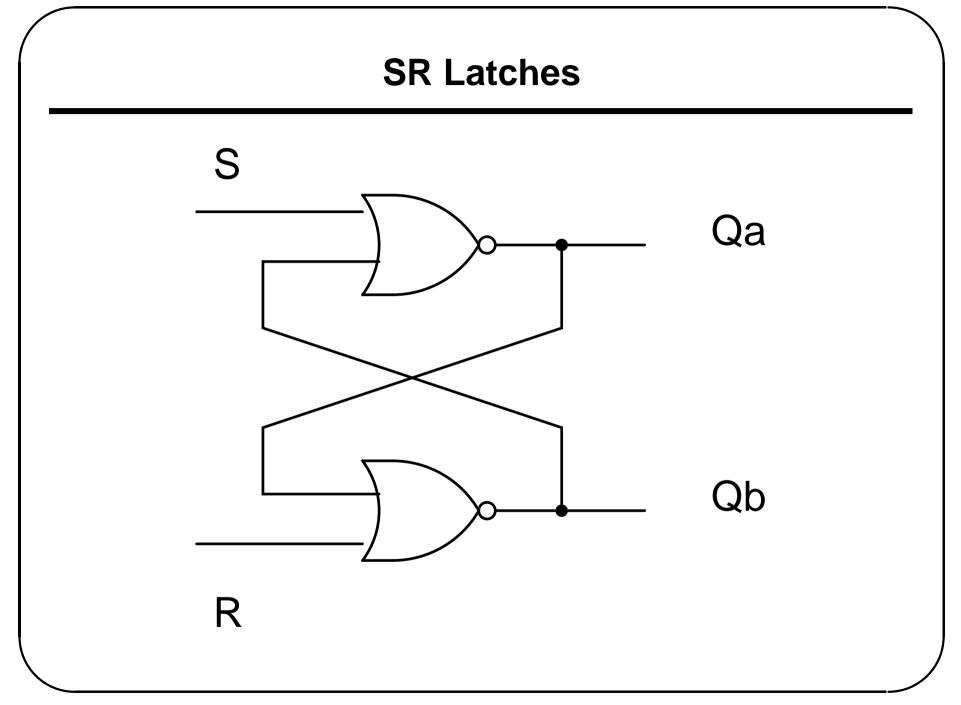

- We shall require a NOR gate to give examples ...

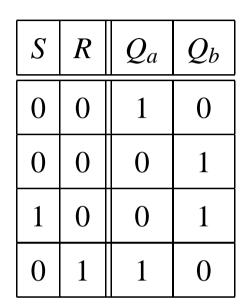

| S | R | $Q_a$ | $Q_b$ |

|---|---|-------|-------|

| 0 | 1 | 0     | 1     |

| 0 | 0 | 1     | 1     |

Stable States

Unstable States

*S* is the **set** line and *R* the **reset** line.  $Q_b$  is a signal which can be set (to 1) and reset (to 0).  $Q_b$  will be used as a 1 bit memory.

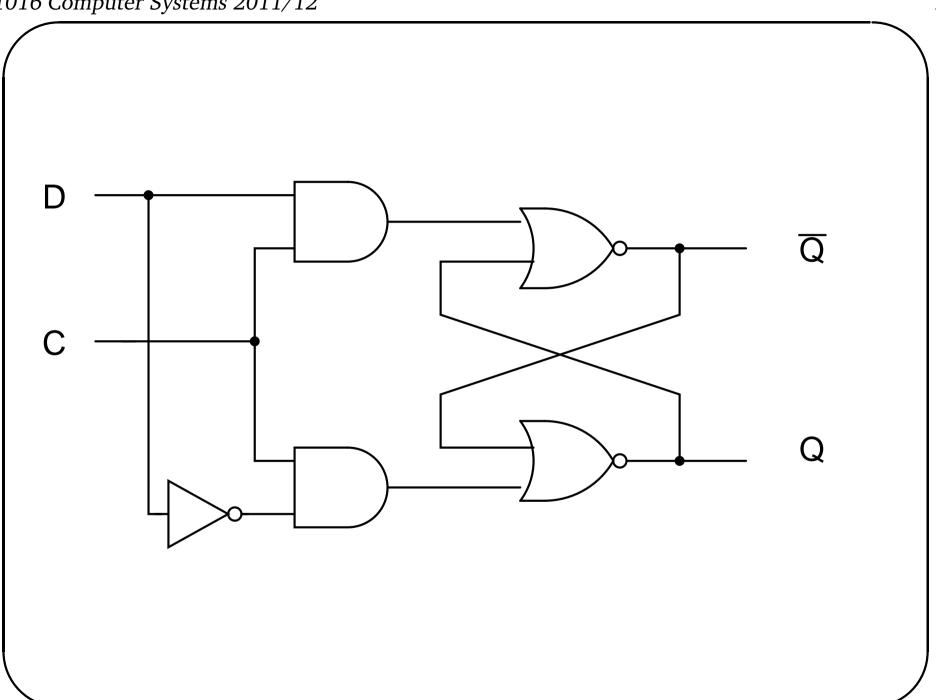

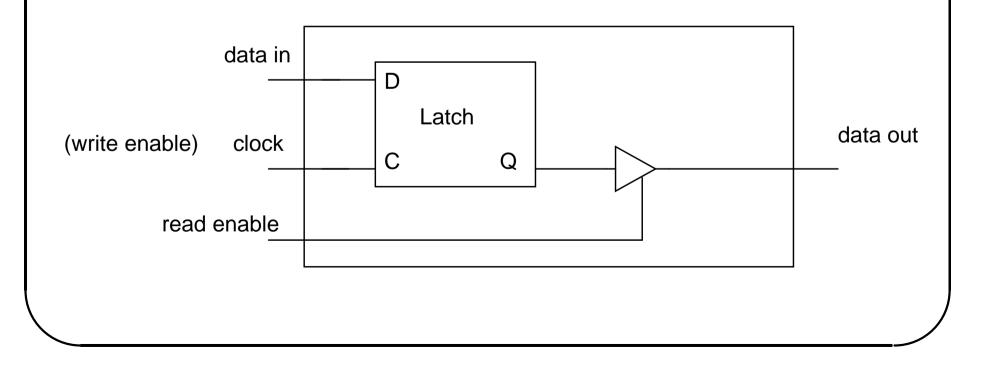

### **Clocked D Latches**

- A model of 1-bit computer memory is a pad-locked box storing 0s and 1s. The box has a glass window.

- *Note: The words input/write/store mean the same* thing. The same goes for **output/read**.

- data line D provides the data (0 or 1) which we want to store.

- **clock line** indicates when data can and cannot be stored—a write enable line.

- $\blacksquare$  Q holds the stored data.

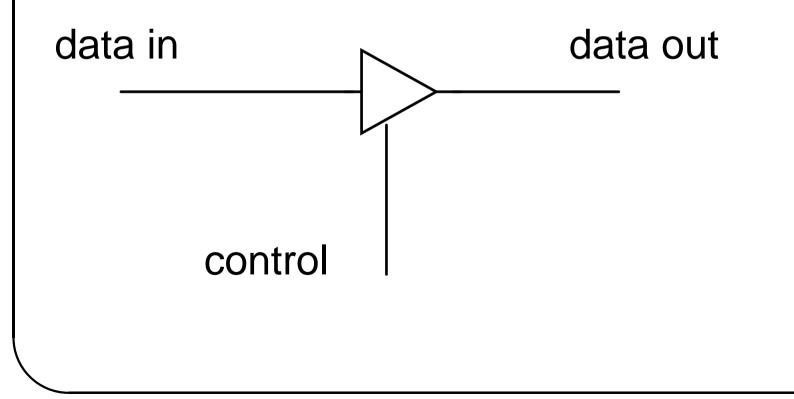

- A Tri State Buffer is an electronic switch.

- We use it to make a **read enable** line for a 1-bit memory.

### Example

Explain how to produce a 1-bit memory which has a read enable line; only when the line is high should the stored data be readable. Answer:

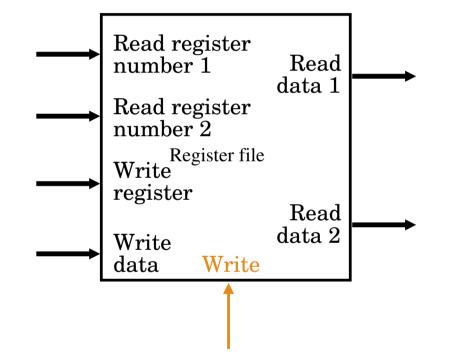

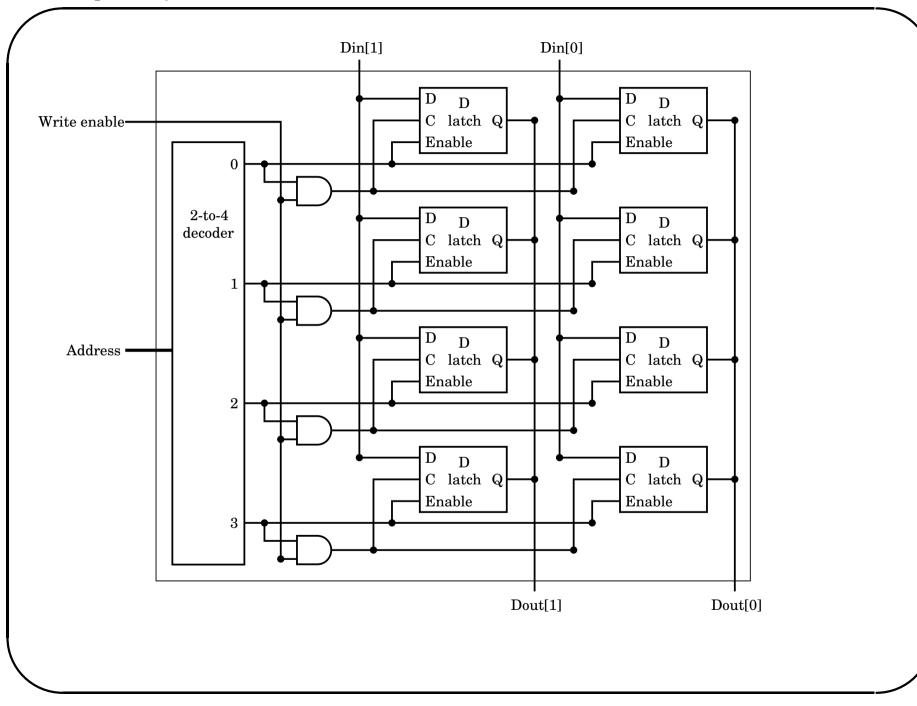

## **Register Files**

- A *k*-bit register is k 1-bit memories which have their clock lines wired together to form a **write** enable line.

- A **register file** (for a CPU) consists of

- a set of *k*-bit registers;

- a set of **read-register** busses and a set of **read-data** busses;

- a set of **write-register** busses and a set of **write-data** busses; and

- a **write enable** line.

#### *Reading from/ Writing to the Register File:*

(COPYRIGHT 1998 MORGAN KAUFMANN PUBLISHERS, INC. ALL RIGHTS RESERVED.)

Computers count in binary.

| Kilo (K) | 2 <sup>10</sup> |

|----------|-----------------|

| Mega (M) | $2^{20}$        |

| Giga (G) | $2^{30}$        |

| Tera (T) | 2 <sup>40</sup> |

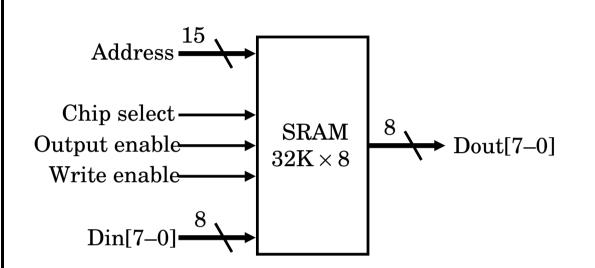

- The number of bits in a cell is sometimes called the chip's width, and the number of cells its height.

- We talk about an  $h \times w$ -SRAM.

CO1016 Computer Systems 2011/12

MIPS R2000 provides a 32-bit computer:

- CPU registers have 32 bits.

- Instructions stored in 32-bit main memory word locations.

- Main memory cells have 8 bits: byte locations.

- Each register is denoted by a special (assembly language) symbol. Eg \$s4.

- We identify a register by its assembly symbol (eg \$s4) or **register number** (CPU address), 0 to 31.

- The binary representations of 0 to 31 are the machine language register numbers for the 32 registers.

- Note: The MIPS R2000 has 32 registers, and each register has 32 bits. Do not let this confuse you!

MIPS R2000 instructions have two forms, machine language and assembly language.

- MIPS ISA assembly example add \$t0, \$t1, \$t2.

- There is a machine language form

| _      | \$t1   | \$t2   | \$t0   | _      | add    |

|--------|--------|--------|--------|--------|--------|

| 000000 | 01001  | 01010  | 01000  | 00000  | 100000 |

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

Each section is called a **field**.

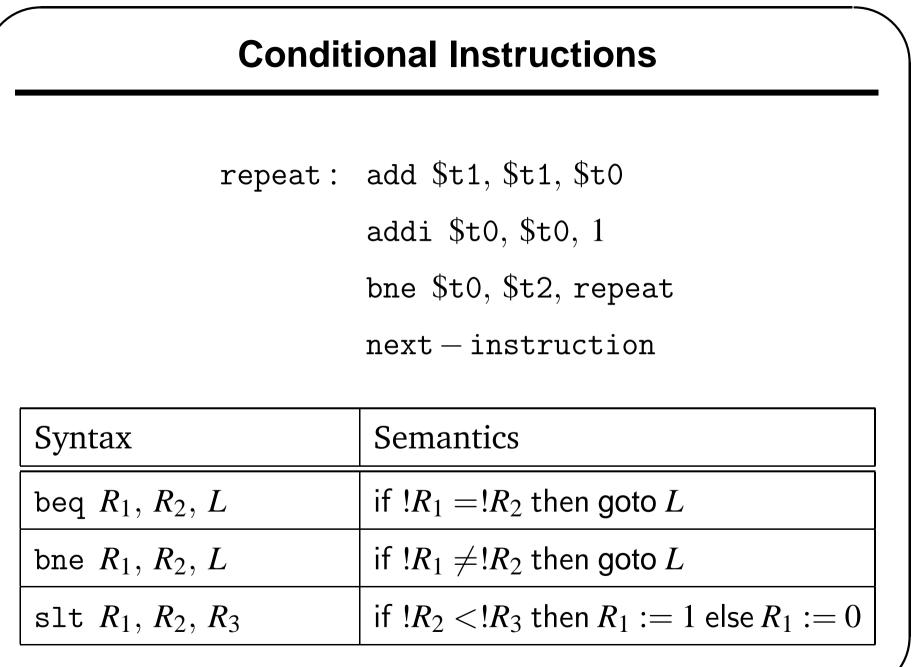

addi \$t0, \$zero, 0 begin: addi \$t1, \$zero, 0 addi \$t2, \$zero, 8 repeat: add \$t1, \$t1, \$t0 addi \$t0, \$t0, 1 bne \$t0, \$t2, repeat sw \$t1, 0, \$t3 finish:

- You will understand the details of CPU registers.

- You will learn about different ways of reading/writing data between CPU and main memory.

- Learn some assembly instructions; SYNTAX and SEMANTICS.

- Show that the instructions can be grouped into *categories*.

- *R* denotes any MIPS register.

- To describe ISA semantics we shall use **assignments**.

- An assignment takes the form  $R := \omega$  (eg  $t1 := \vec{0}$ )

- If the register has k bits, the word  $\omega$  is a sequence of k binary digits.

- We will stick to k = 32.

- We will adopt a convention. We may write things like R := 7. The convention is that this will be shorthand for  $R := \vec{0}111^{bin}$ .

- We can describe the semantics of the instruction add  $R_1$ ,  $R_2$ ,  $R_3$  as

$R_1 := !R_2 + !R_3$

$!R_2+!R_3$  is given by (32 digit) digitwise sum.

- B[a] is the byte location at main memory address a.

- We have a similar notation W[a] for word locations.

- Program instructions stored in consecutive word locations in main memory.

- Recall cells are 8 bits. So addresses of word locations are multiples of 4. (IMPORTANT!!)

The MIPS R2000 is big endian format.

### Introduction to Addressing

- Addressing refers to the ways in which data is read/written.

- Data copied from main memory into a register is **loaded**.

- Data copied from a register into main memory is **stored**.

- These forms of copying are **data transfers**.

#### Consider the two instructions

addi  $R_1, R_2, 5$  add  $R_1, R_2, R_3$

We refer to add and addi as instruction **names**.

■ The registers *R<sub>i</sub>* and the integer 5 are called instruction **arguments**.

■ The arguments tell us *where* data is read from or written (stored) to.

■  $R_2$  and  $R_3$  contain data to be (read and) added. We call them **source** arguments.

$\blacksquare R_1 \text{ specifies where the result is to be stored. We shall call it a$ **destination**argument.

■ Finally, we refer to the numbers to be added as **operands**.

- The data is specified as part of the instruction.

- For example 24 in addi \$t0, \$t1, 24.

- The semantics of the instruction is given by t0 := !\$t1 + 24.

- We sometimes refer to data (operands) given by immediate addressing as **constants**.

- + means digitwize sum; 24 is stored in binary.

- The data is given as the contents of a register.

- If the register is called *R*, the data is !*R*.

- add uses register addressing for its source arguments.

- I The semantics of add \$t0, \$t1, \$t2 is

\$t0:=!\$t1+!\$t2

- The data specified by R is !W[!R] or !B[!R]

- In this case, we refer to *R* as a **pointer**.

- Often need to load a sequence of words from memory, all "quite near" to a **base** address *k*.

- An **offset** indicates how far data is located from the base address. The offset equals !R.

- Instructions have a source argument k(R).

- The source data is given by the contents of W[!R+k].

k has denoted any integer.

■ So !*R*+*k* means add the 32 digits of !*R* to a 32 digit 2s-complement representation of *k*.

The machine code field for  $k \in \mathbb{Z}$  is only 16 bits!!

■ A 16-bit representation of *k* will be copied into a 32-bit ALU. This will involve a sign extension.

Note that

$$-2^{15} \le k \le 2^{15} - 1$$

#### **Arithmetic Category Instructions**

| Syntax              | Semantics             |  |

|---------------------|-----------------------|--|

| add $R_1, R_2, R_3$ | $R_1 := !R_2 + !R_3$  |  |

| sub $R_1, R_2, R_3$ | $R_1 := !R_2 - !R_3$  |  |

| addi $R_1, R_2, k$  | $R_1 := !R_2 + sx(k)$ |  |

See example ...

### **Data Transfer Instructions**

| Syntax           | Semantics                   |

|------------------|-----------------------------|

| lw $R_1, k(R_2)$ | $R_1 := !W[sx(k) + !R_2]$   |

| sw $R_1, k(R_2)$ | $W[sx(k) + !R_2] := !R_1$   |

| lb $R_1, k(R_2)$ | $R_1 := sx(!B[sx(k)+!R_2])$ |

#### **Overview: MIPS Machine Language**

- Explain how to represent the ISA assembly instructions inside the machine as binary digit sequences (machine code).

- Each digit sequence is made up of special parts, called fields. We give an algorithm for working out what the fields are.

- Look at how to translate branch labels into actual machine addresses.

#### **Instruction Fields**

- Given any MIPS instruction, what is the corresponding 32-bit machine language instruction?

- Each machine instruction belongs to one of three formats. These are know as R, I and J formats.

- Each format has a **field layout**, specifying how the 32 bits are divided up into sections known as **fields**.

### **R-Format**

Here is a field layout for *name*  $R_1$ ,  $R_2$ ,  $R_3$

| Fields    |        |        |        |           |        |

|-----------|--------|--------|--------|-----------|--------|

| op        | rs     | rt     | rd     | shamt     | funct  |

| 6 bits    | 5 bits | 5 bits | 5 bits | 5 bits    | 6 bits |

| $\vec{0}$ | $R_2$  | $R_3$  | $R_1$  | $\vec{0}$ | name   |

| $\vec{0}$ | \$s1   | \$s2   | \$t0   | $\vec{0}$ | add    |

| 000000    | 10001  | 10010  | 01000  | 00000     | 100000 |

■ For R-format instructions the Opcode (op) is 0<sup>*dec*</sup>.

■ The Function field (funct) is derived from the instruction name add. There is a look-up table in the notes ...

■ The rs and rt fields specify the *numbers* of the source registers (17<sup>*dec*</sup> and 18<sup>*dec*</sup>)

■ The rd field, 8<sup>*dec*</sup>, specifies the *number* of the destination register.

Finally, the shamt field is ALWAYS set to  $0^{dec}$  in CO1016.

# **I-Format**

Here is a field layout for *name*  $R_1$ ,  $k(R_2)$

| ор                                   | rs     | rt     | address |

|--------------------------------------|--------|--------|---------|

| 6 bits                               | 5 bits | 5 bits | 16 bits |

| addi, andi, ori, lw, sw, lb, lbu, sb | $R_2$  | $R_1$  | k       |

#### Register number table on page 79 of the notes.

| Register Usage |    | Usage                                            |

|----------------|----|--------------------------------------------------|

| \$zero         | 0  | contents always zero                             |

| \$v0           | 2  | expression evaluation and function results       |

| \$v1           | 3  | expression evaluation and function results       |

| \$a0           | 4  | first argument component (preserved across call) |

| \$t0           | 8  | temporary (not preserved across call)            |

| \$t1           | 9  | temporary (not preserved across call)            |

| \$t2           | 10 | temporary (not preserved across call)            |

| \$fp           | 30 | frame pointer (preserved across call)            |

## Example

What is the machine code for lw \$s1, 8(\$t1) ?

- name  $R_1$ ,  $k(R_2)$  is I-format.

- Use look-up table for 1w opcode: 35.

- Use register number table for \$s1: 17 and for \$t1: 9.

| 6 bits | 5 bits | 5 bits | 16 bits         |

|--------|--------|--------|-----------------|

| lw     | $R_2$  | $R_1$  | k               |

| 100011 | 01001  | 10001  | 000000000001000 |

### **Machine Code for Branches**

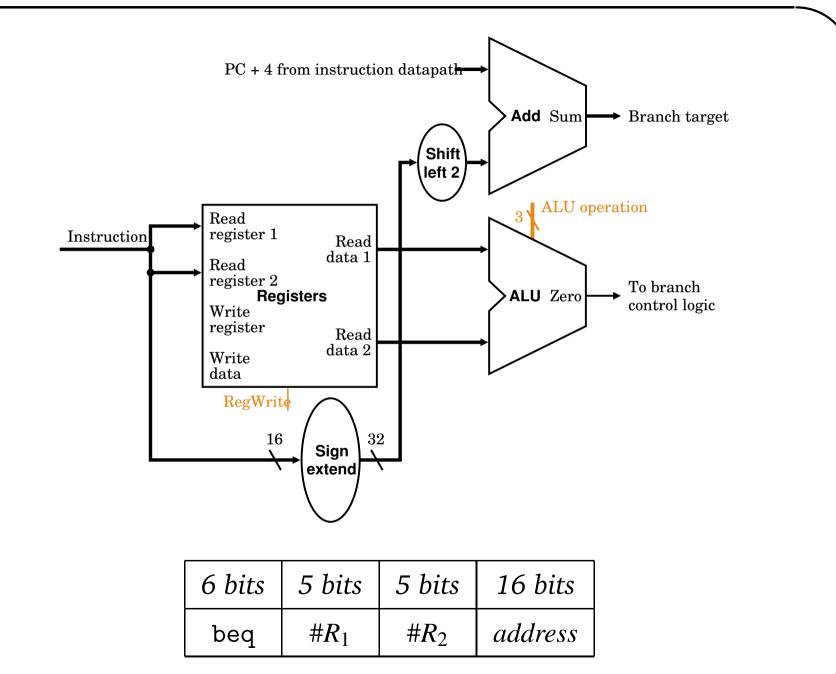

- Recall beq  $R_1, R_2, L$ .

- $!R_1 = !R_2$  TRUE: the *label* L "*points*" to the next instruction to be executed.

- $!R_1 = !R_2$  FALSE: execute *next instruction in memory*.

- Such instructions are I-format:

| op     | rs     | rt     | address |

|--------|--------|--------|---------|

| 6 bits | 5 bits | 5 bits | 16 bits |

| beq    | $R_1$  | $R_2$  | L       |

• Looking up the opcode and register numbers is easy!

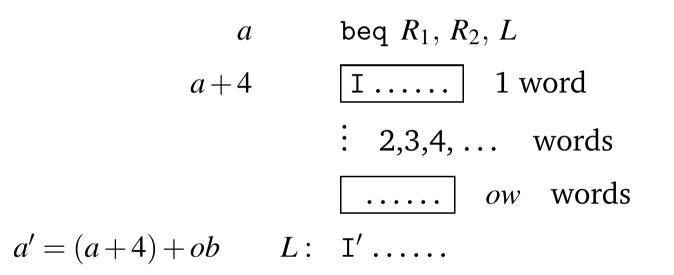

The address field specifies the distance (offset) ow in words from the address of the *next instruction* I *in memory* to the address of the labelled **instruction** I'

$$a \qquad beq R_1, R_2, L$$

$$a+4 \qquad \boxed{\texttt{I} \dots \texttt{I}} \quad 1 \text{ word}$$

$$\vdots \quad 2,3,4, \dots \quad words$$

$$a' \quad L: \quad \texttt{I}' \dots \texttt{I}$$

To be precise  $ow = (|address|) \in \mathbb{Z}$  words. *Thus we can work out the address field*. See my example on the OHP . . . if  $ow = 2 \in \mathbb{Z}$ , address = 00000000000000010  $\in \mathbb{B}^{16}$ .

What about the address *a*′ of the labelled instruction?

Addresses count cells (bytes); each word location consists of four cells. So

$$ob = 4 * ow = 4 * (|address|) \in \mathbb{Z}$$

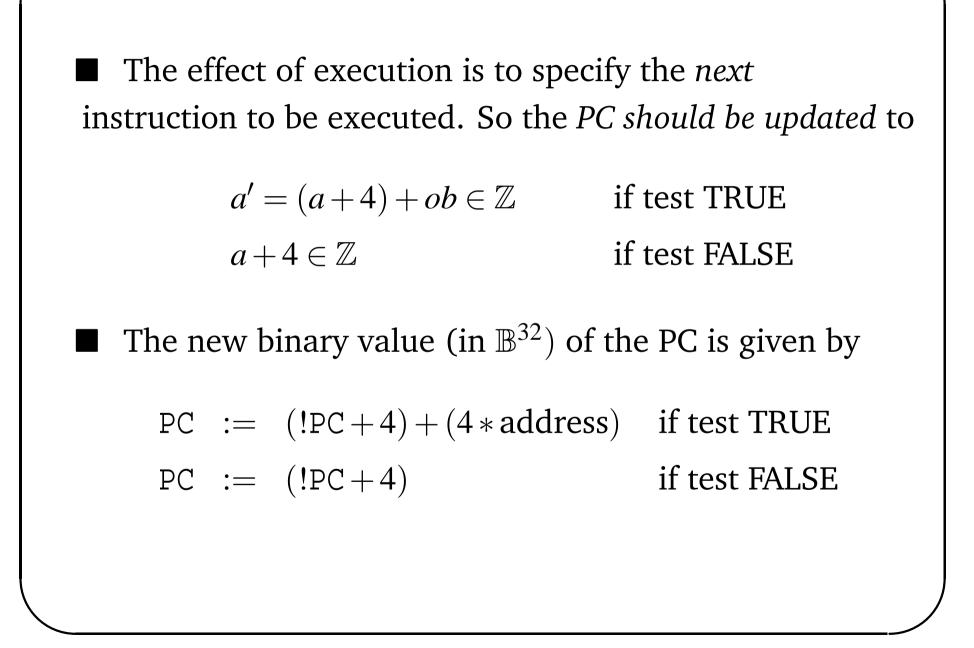

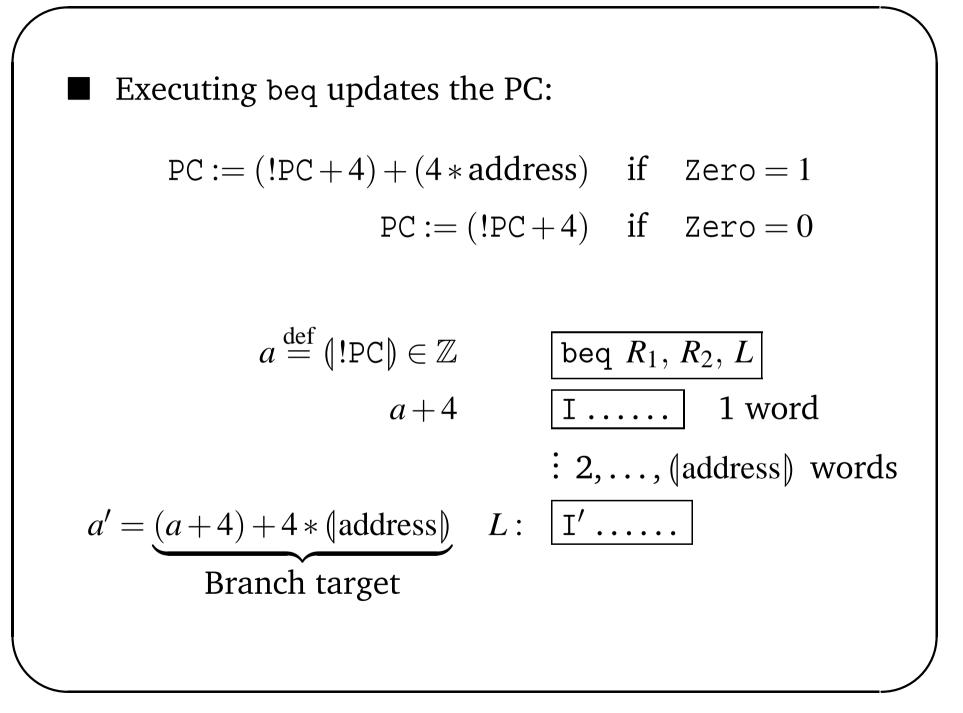

#### **Branch Semantics at Run Time**

■ The last section explained how to work out the machine code for a branch instruction with label *L* by using the position of the instruction labelled *L*.

Suppose we know the machine code for a branch.

What happens at run time? Recall the SEMANTICS

if  $!R_1 = !R_2$  then goto L

As beq  $R_1$ ,  $R_2$ , L STARTS to execute, suppose the PC contains  $a \in \mathbb{Z}$ .

# Chapter 6

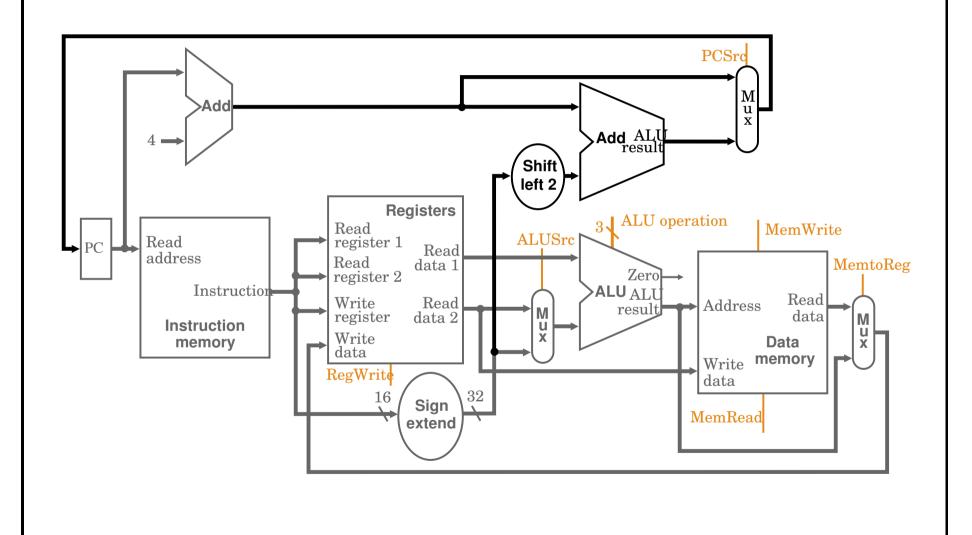

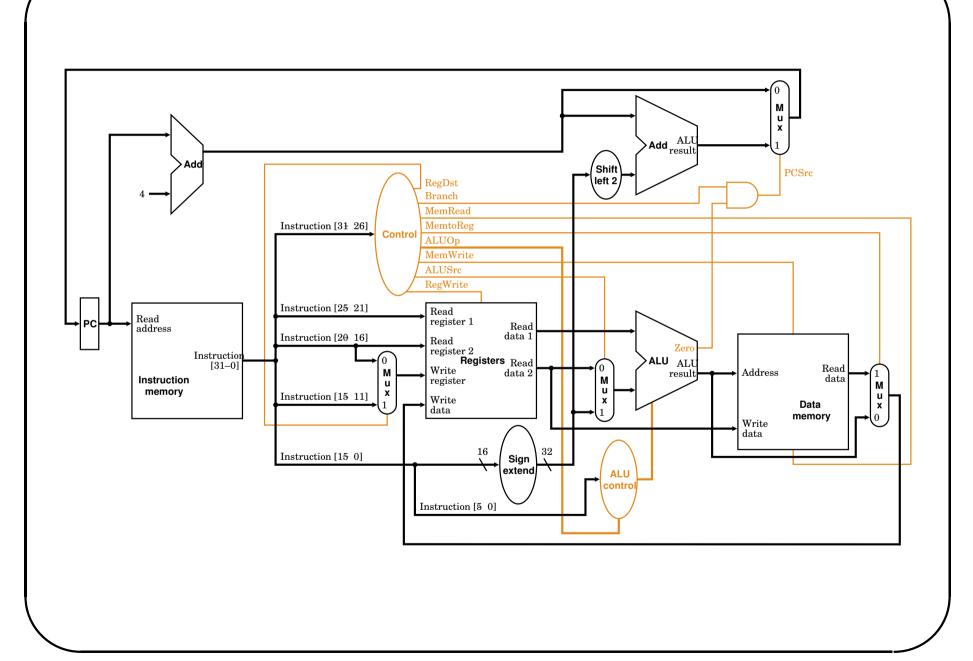

Build a datapath in which each ISA instruction is executed in one clock cycle.

Design control for this.

In notes; non-examinable:

Build a datapath in which each ISA instruction requires many clock cycles for execution, but the amount of hardware is reduced.

Design control for this.

### Introduction

- Show how to build a small CPU = datapath + control.

- Design of the CPU is called its **architecture**.

- Micro refers to CPU design, not overall computer design.

- We shall develop a micro architecture for

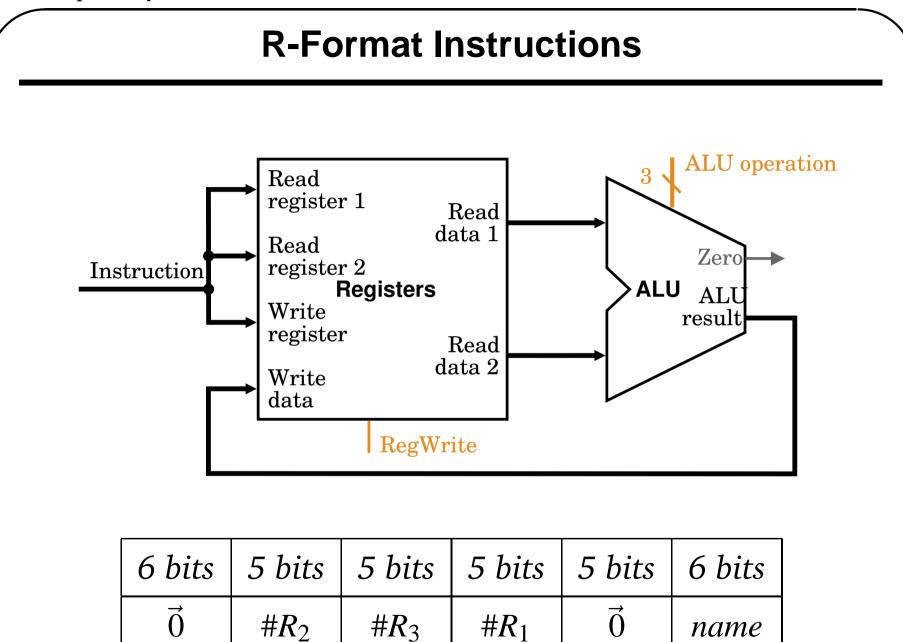

- The R-format instructions add, sub, and, or, and slt;

- the I-format instructions lw, sw, and beq.

## **Overview: Datapath Components**

■ We give examples of the circuits in a datapath responsible for the execution of different categories of instruction.

CO1016 Computer Systems 2011/12

155

These have the form *name*  $R_1$ ,  $R_2$ ,  $R_3$ .

- Machine instruction  $I[31-0] \in \mathbb{B}^{32}$  passed along 32-bit wide Instruction bus; the fields are divided up ...

- The numbers of  $R_2$  and  $R_3$  ie  $I[25-21] \in \mathbb{B}^5$  and  $I[20-16] \in \mathbb{B}^5$  are passed along 5-bit Read register 1 and Read register 2. These are source registers.

■ Destination register number  $I[15 - 11] \in \mathbb{B}^5$  passed along 5 bit Write register bus.

- Source operands  $!R_1$  and  $!R_2$  appear on the 32-bit Read data 1 and Read data 2

- ALU operation is set by control and result is written ...

CO1016 Computer Systems 2011/12

#### **Load/Store Instructions**

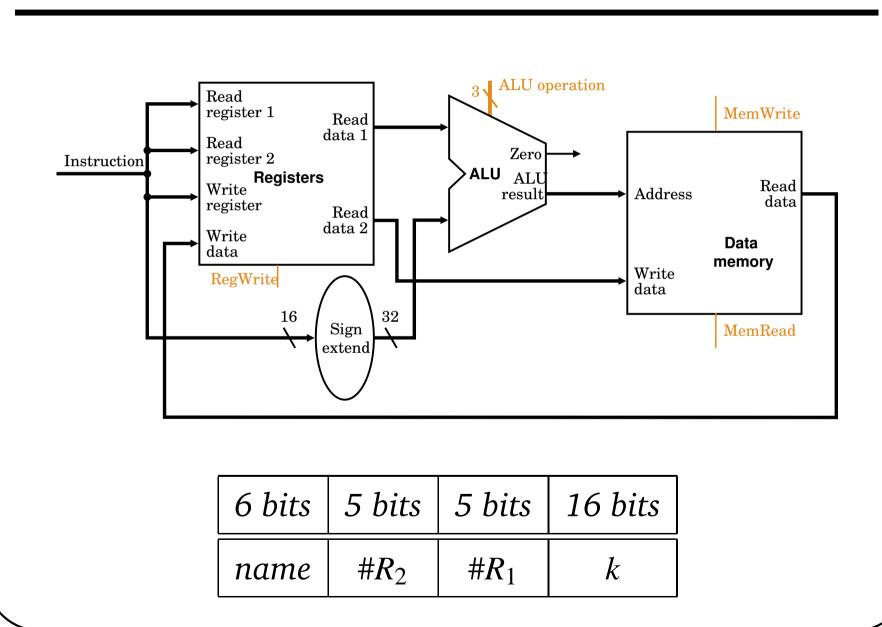

- We examine  $lw R_1$ ,  $k(R_2)$  where  $R_1 := !W[!R_2 + sx(k)]$ .

- The number of register  $R_2$  ie  $I[25-21] \in \mathbb{B}^5$  goes to Read register 1

- 16-bit representation of k ie  $I[15-0] \in \mathbb{B}^{16}$  goes to Sign extend.

- Contents of  $R_2$  go via Read data 1 to ALU, along with sign extended k.

- Data memory gets Address  $a \stackrel{\mathrm{def}}{=} !R_2 + sx(k) \in \mathbb{B}^{32}.$

Data memory sends the contents of the word at a via Read data into register file Write data.

Register number of  $R_1$  ie  $I[20 - 16] \in \mathbb{B}^5$  is in Write register, so  $!W[a] \in \mathbb{B}^{32}$  is written in  $R_1$ .

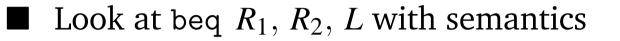

if  $!R_1 = !R_2$  then goto L

Need to check if  $!R_1 = !R_2$  is true or false ...

ALU calculates

$$\vec{r} \stackrel{\text{def}}{=} !R_1 - !R_2$$

. Zero tests if  $\vec{r} = \vec{0}$ .

| $!R_1 = !R_2$ | $\vec{r} \stackrel{\text{def}}{=} !R_1 - !R_2$ | Zero |

|---------------|------------------------------------------------|------|

| True          | $=\vec{0}$                                     | 1    |

| False         | $ eq \vec{0}$                                  | 0    |

■ There is a control PCSrc for a multiplexor. In fact (see later on) PCSrc is set equal to Zero when a branch instruction is executed.

- So if PCSrc=Zero=0 then the PC *will—see circuit*—be updated with !PC+4.

- And if PCSrc=Zero=1 the PC is updated with  $(!PC+4) + (sx(I[15-0]) \ll 2) = (!PC+4) + (4 * address).$

Eg  $1011 \ll 2 \stackrel{\text{def}}{=} 1011.00$  and

$$(1011.00) = -20 = 4 * -5 = 4 * (1011)$$

■ We assemble the datapath components into a single cycle datapath (each instruction takes one clock cycle).

We design a control unit.

# **Building Control**

We decide on the *effects* on the datapath that actual control signals must have.

We then draw up truth tables of control signal values to ensure that various instructions are executed.

|       |                            |   |   |   |    |    |                         | Settings for control of |              |          |         |          |        |        |        |

|-------|----------------------------|---|---|---|----|----|-------------------------|-------------------------|--------------|----------|---------|----------|--------|--------|--------|

|       |                            |   |   |   |    |    | multiplexors and memory |                         |              |          |         |          |        |        |        |

|       |                            |   |   |   |    |    | re                      | ead/v                   | <u>write</u> | enat     | ole     |          |        |        |        |

|       |                            |   |   |   |    |    | RegDst                  | ALUSrc                  | MemtoReg     | RegWrite | MemRead | MemWrite | Branch | ALUOp1 | ALUOp2 |

| Inst  | Opcode field =<br>I[31-26] |   |   |   | Re | AL | Me                      | Re                      | Me           | Me       | Bra     | AL       | AL     |        |        |

| 1w    | 1                          | 0 | 0 | 0 | 1  | 1  | 0                       | 1                       | 1            | 1        | 1       | 0        | 0      | 0      | 0      |

| SW    | 1                          | 0 | 1 | 0 | 1  | 1  | X                       | 1                       | Х            | 0        | 0       | 1        | 0      | 0      | 0      |

| beq   | 0                          | 0 | 0 | 1 | 0  | 0  | X                       | 0                       | Х            | 0        | 0       | 0        | 1      | 0      | 1      |

| R-f't | 0                          | 0 | 0 | 0 | 0  | 0  | 1                       | 0                       | 0            | 1        | 0       | 0        | 0      | 1      | 0      |

| Instruction<br>(ALU operation) | ALUOp1 | ALUOp2 | Funct Field = I[5-0] |   |   |   |   | ALU-Control | ALU-Control<br>Output:<br>sets ALU<br>operations |   |   |  |

|--------------------------------|--------|--------|----------------------|---|---|---|---|-------------|--------------------------------------------------|---|---|--|

| lw/sw (+)                      | 0      | 0      | X X X X X X          |   |   |   | 0 | 1           | 0                                                |   |   |  |

| beq (-)                        | 0      | 1      | X                    | Χ | Х | Х | Х | Χ           | 1                                                | 1 | 0 |  |

| add (+)                        | 1      | 0      | 1                    | 0 | 0 | 0 | 0 | 0           | 0                                                | 1 | 0 |  |

| sub (-)                        | 1      | 0      | 1                    | 0 | 0 | 0 | 1 | 0           | 1                                                | 1 | 0 |  |

| or ( <i>OR</i> )               | 1      | 0      | 1                    | 0 | 0 | 1 | 0 | 1           | 0                                                | 0 | 1 |  |

| slt (Less)                     | 1      | 0      | 1                    | 0 | 1 | 0 | 1 | 0           | 1                                                | 1 | 1 |  |

- Explain the timing and performance of a processor.

- Give equations for processor performance.

Recall that a *clock* generates pulses, each lasting for a fixed period of time.

• Clock period called a **cycle**.

■ Control unit will set datapath elements, using their control busses (eg ALU to +), once per cycle.

■ If an instruction can be executed in one clock cycle, we call it a **single cycle instruction**.

- If a datapath can execute each instruction in one cycle, we call it a **single cycle datapath**.

- If a datapath requires multiple settings to execute at least some instructions, we call it a **multi cycle datapath**.

- We look at timing issues for a multicycle processor.

An instruction requires a number of clock cycles to execute. Called the **cycles per instruction** or **CPI**. Write  $C_I$  for the CPI of instruction *I*.

A 6 instruction program P

| Instruction I | class | cycles C <sub>I</sub> |  |  |  |  |  |

|---------------|-------|-----------------------|--|--|--|--|--|

| lw            | α     | 4                     |  |  |  |  |  |

| lw            | α     | 4                     |  |  |  |  |  |

| add           | β     | 5                     |  |  |  |  |  |

| sub           | β     | 5                     |  |  |  |  |  |

| bne           | γ     | 6                     |  |  |  |  |  |

| SW            | α     | 4                     |  |  |  |  |  |

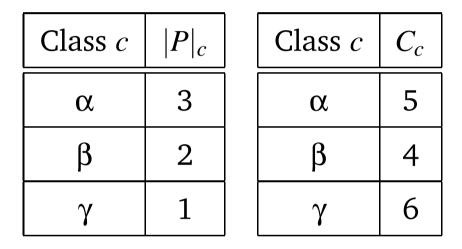

Write  $|P|_c$  for the number of instructions in *P* of class *c* and *C<sub>c</sub>* for the number of cylces to run any class *c* instruction.

Thus the number of clock cycles to execute *P* is

Total Clock Cycles =  $C_P = (3*5) + (2*4) + (1*6) = 29$

■ Write  $Cl_{CPI}(P)$  for the set of classes of instructions with identical CPI in a program *P*.

Total Clock Cycles

$$= C_P \stackrel{\text{def}}{=} \sum_{c \in Cl_{CPI}(P)} |P|_c * C_c$$

• We shall write  $\pi$  for a clock period. Of course

$$t_P = C_P * \pi \qquad t_I = C_I * \pi$$

It also follows that the time taken to execute *P* is

$$t_P = \left(\sum_{c \in Cl_{CPI}(P)} |P|_c * C_c\right) * \pi$$