## Internal memory sorting and searching

Ву

#### Naila Yasmeen Rahman

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in Computer Science

2002

King's College University of London

### Abstract

In this thesis we consider methods of designing fast, practical algorithms for sorting and searching data in the main memory of a computer system. Algorithms are traditionally analysed on the Random Access Machine (RAM) model, but such analyses often give inaccurate predictions of performance. This is partially due to the fact that the RAM model assumes the same time for arithmetic operations and memory accesses, while on today's computer systems a main memory access may take more than 100 times as long as an arithmetic operation, and this difference is likely to increase in the future. To minimise main memory accesses computer systems use one or more fast, small memories called caches, which store copies of recently accessed data. The RAM model also does not capture the translation of virtual memory addresses into physical memory addresses. Computer systems use a specialised, fast, small memory called the translation-look-aside buffer (TLB) to facilitate such translations.

Main memory, caches and the TLB constitute the internal memory hierarchy, while main memory, fast external memory (disks) and slow external memories (such as tapes) can be referred to as the external memory hierarchy. The main challenge in designing fast algorithms for the internal memory hierarchy is to minimise the number of cache and TLB misses, that is the number of accesses to data which are not in the cache or TLB. We show how algorithms and their analyses for the external memory hierarchy can be converted to corresponding algorithms and analyses for the internal memory hierarchy. We are the first to systematically consider TLB misses in this context.

We then consider the problems of sorting independent random floating-point numbers using distribution sorting and sorting integers using radix sort. We analyse the number of cache and TLB misses for these problems and design algorithms which comprehensively outperform Quicksort. We also analyse the number of cache and TLB

misses for search tree data structures and design new search tree data structures that outperform existing ones.

We include extensive experimental results, which support the presented analyses.

## **Declaration**

I declare that this doctoral thesis was composed by myself and the work contained herein is my own, except as stated now. Some parts of the thesis contain work from the following jointly-authored papers:

- [70] N. Rahman, R. Cole and R. Raman. Optimising Predecessor Data Structures for Internal Memory. In Proc. 5th International Workshop on Algorithm Engineering, LNCS 2141, pp. 67–78, 2001.

- [71] N. Rahman and R. Raman. Analysing Cache Effects in Distribution Sorting. ACM Journal of Experimental Algorithmics 5, Article 14, 2001. Preliminary version in Proc. 3rd Workshop on Algorithm Engineering, LNCS 1668, pp. 184– 198, 1999.

- [72] N. Rahman and R. Raman. Adapting radix sort to the memory hierarchy. ACM Journal of Experimental Algorithmics, (to appear). Preliminary version in Proc. 2nd Workshop on Algorithm Engineering and Experiments, 2000.

- [73] N. Rahman and R. Raman. Analysing the Cache Behaviour of Non-uniform Distribution Sorting Algorithms. In Proc. 8th Annual European Symposium on Algorithms, LNCS 1879, pp. 380–391, 2000.

## Acknowledgements

I am extremely grateful to my supervisor, Prof. Rajeev Raman. Rajeev got me started in this area of research and has given me constant support and encouragement throughout my PhD studies. He has taught me how to do the highest quality research.

I would especially like to thank my husband, Tomasz Radzik, for his love and support. I would also like to thank Tomek for reading and commenting on the various drafts of the thesis.

I would like to thank the EPSRC for the PhD studentship. Without their financial support, completing my research in any reasonable timeframe would have been very difficult.

I owe many thanks to my friends and colleagues at Avaya Communications for their support over the years. I would also like to thank the management at Avaya for always allowing me to work there when other sources of funding were unavailable.

I would also like to thank my friends and family for their encouragement. Most importantly, I would like to thank my parents for their love and guidance.

## Contents

| 1                                  | Intr           | roducti | ion                                 | 15 |

|------------------------------------|----------------|---------|-------------------------------------|----|

|                                    | 1.1            | Intern  | al memory hierarchy                 | 20 |

|                                    |                | 1.1.1   | Caches                              | 20 |

|                                    |                | 1.1.2   | TLB                                 | 20 |

|                                    | 1.2            | Sortin  | g and searching                     | 22 |

|                                    |                | 1.2.1   | Sorting random numbers              | 22 |

|                                    |                | 1.2.2   | Sorting integers                    | 23 |

|                                    |                | 1.2.3   | Searching                           | 24 |

|                                    | 1.3            | Metho   | odology                             | 24 |

|                                    | 1.4            | Contr   | ibutions of the thesis              | 26 |

|                                    | 1.5            | Organ   | isation of the thesis               | 27 |

| 2                                  | $\mathbf{Pre}$ | vious   | work                                | 29 |

|                                    | 2.1            | Memo    | ory Models                          | 30 |

|                                    |                | 2.1.1   | Discrete hierarchical memory models | 30 |

|                                    |                | 2.1.2   | Smooth hierarchical memory models   | 34 |

|                                    |                | 2.1.3   | Cache-Oblivious Model               | 36 |

|                                    |                | 2.1.4   | Cache Memory Model (CMM)            | 39 |

| 2.2 Algorithms for internal memory |                | Algori  | ithms for internal memory           | 41 |

|                                    |                | 2.2.1   | System support                      | 41 |

|                                    |                | 2.2.2   | Algorithms                          | 43 |

|                                    | 2.3            | Cache   | misses and power consumption        | 46 |

|                                    | 0.4            | a       |                                     | 45 |

| 3                                          | Inte                                                             | ernal N                                       | Memory Model and emulations                                     | 48 |  |  |

|--------------------------------------------|------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------|----|--|--|

|                                            | 3.1                                                              | Internal Memory Model (IMM)                   |                                                                 |    |  |  |

|                                            |                                                                  | 3.1.1                                         | Criticisms of the model                                         | 50 |  |  |

|                                            |                                                                  | 3.1.2                                         | Designing and evaluating internal memory algorithms             | 51 |  |  |

|                                            | 3.2                                                              | Sun U                                         | ItraSparc-II                                                    | 51 |  |  |

|                                            | 3.3                                                              | Emula                                         | ations                                                          | 52 |  |  |

|                                            |                                                                  | 3.3.1                                         | Emulation of EMM algorithm                                      | 53 |  |  |

|                                            |                                                                  | 3.3.2                                         | Emulation of 3-EMM algorithms                                   | 55 |  |  |

|                                            | 3.4                                                              | Gener                                         | al techniques to obtain simultaneous cache and TLB optimality . | 56 |  |  |

|                                            | 3.5                                                              | Summ                                          | nary                                                            | 57 |  |  |

| 4                                          | Sor                                                              | ting ar                                       | nd searching                                                    | 58 |  |  |

|                                            | 4.1                                                              | Sortin                                        | g                                                               | 58 |  |  |

|                                            |                                                                  | 4.1.1                                         | Lower bounds for sorting                                        | 59 |  |  |

|                                            | 4.2                                                              | Distri                                        | bution sorting                                                  | 60 |  |  |

|                                            |                                                                  | 4.2.1                                         | Count phase                                                     | 61 |  |  |

|                                            |                                                                  | 4.2.2                                         | Permute phase                                                   | 61 |  |  |

|                                            | 4.3                                                              | Radix                                         | sorting                                                         | 65 |  |  |

|                                            | 4.4                                                              | Bundle sorting                                |                                                                 |    |  |  |

|                                            | 4.5                                                              | Multi-partition Quicksort and k-way Mergesort |                                                                 |    |  |  |

|                                            | 4.6                                                              | Search                                        | ning                                                            | 68 |  |  |

|                                            |                                                                  | 4.6.1                                         | B-trees                                                         | 69 |  |  |

|                                            |                                                                  | 4.6.2                                         | $B^*$ -trees                                                    | 70 |  |  |

| 5                                          | Analysing the permute phase of distribution sorting in the CMM 7 |                                               |                                                                 |    |  |  |

|                                            | 5.1                                                              | Proces                                        | sses                                                            | 72 |  |  |

|                                            |                                                                  | 5.1.1                                         | Process to model an in-place permutation                        | 72 |  |  |

|                                            |                                                                  | 5.1.2                                         | Process to model an out-of-place permutation                    | 73 |  |  |

|                                            | 5.2                                                              | Prelin                                        | ninaries                                                        | 75 |  |  |

| 5.3 Cache analysis of in-place permutation |                                                                  | Cache                                         | analysis of in-place permutation                                | 78 |  |  |

|                                            |                                                                  | 5.3.1                                         | Average case analysis                                           | 78 |  |  |

|                                            |                                                                  | 5.3.2                                         | Upper bound                                                     | 81 |  |  |

|                                            |                                                                  | 533                                           | Lower bound                                                     | 84 |  |  |

|   |     | 5.3.4 Upper and lower bounds for uniformly-random data 88         |

|---|-----|-------------------------------------------------------------------|

|   | 5.4 | Cache analysis of out-of-place permutation                        |

|   |     | 5.4.1 Average case analysis                                       |

|   |     | 5.4.2 Upper bound                                                 |

|   |     | 5.4.3 Lower bound                                                 |

|   |     | 5.4.4 Upper and lower bounds for uniformly-random data 96         |

|   | 5.5 | Cache analysis of multiple sequences access                       |

|   | 5.6 | Correspondence between the permute phase and Processes "in-place" |

|   |     | and "out-of-place"                                                |

|   | 5.7 | Summary                                                           |

| 6 | App | proximate analysis and validation of predictions in the CMM 101   |

|   | 6.1 | Approximate analysis                                              |

|   |     | 6.1.1 Dissimilar key and count array element sizes 108            |

|   | 6.2 | Cache simulations                                                 |

|   | 6.3 | Accuracy of predictions                                           |

|   | 6.4 | Heuristic 1 for selection of $k$                                  |

|   | 6.5 | Heuristic 2 for selection of $k$                                  |

|   | 6.6 | Summary                                                           |

| 7 | Sor | ting random numbers in the CMM 114                                |

|   | 7.1 | Cache analysis of count phase                                     |

|   |     | 7.1.1 Dissimilar key and count array element sizes                |

|   | 7.2 | Flashsort                                                         |

|   |     | 7.2.1 Flashsort1                                                  |

|   |     | 7.2.2 Multi-pass algorithm                                        |

|   |     | 7.2.3 Experimental results                                        |

|   |     | 7.2.4 Cache simulations                                           |

|   | 7.3 | MSB radix sort                                                    |

|   |     | 7.3.1 Radix sorting floating-point numbers                        |

|   |     | 7.3.2 Using Quicksort                                             |

|   |     | 7.3.3 Cache analysis                                              |

|   |     | 7.3.4 Tuning MSB radix sort                                       |

|    |      | 7.3.5   | Experimental results                  | 134          |

|----|------|---------|---------------------------------------|--------------|

|    | 7.4  | Summ    | ary                                   | 134          |

| 8  | Sort | ing in  | tegers in the IMM                     | L <b>36</b>  |

|    | 8.1  | Techni  | iques to reduce TLB misses            | 136          |

|    | 8.2  | LSB ra  | adix sort                             | 138          |

|    |      | 8.2.1   | Worst-case cache miss analysis        | 138          |

|    |      | 8.2.2   | Worst-case TLB miss analysis          | 139          |

|    | 8.3  | Imple   | nenting LSB radix sort                | 141          |

|    |      | 8.3.1   | Reducing working set size             | 141          |

|    |      | 8.3.2   | Speeding up the count phase           | 142          |

|    | 8.4  | Explic  | it Block Transfers                    | 143          |

|    |      | 8.4.1   | EBT radix sort                        | 143          |

|    |      | 8.4.2   | Implementing EBT Radix Sort           | 143          |

|    | 8.5  | Pre-so  | rting                                 | 144          |

|    |      | 8.5.1   | PLSB Radix Sort                       | 144          |

|    |      | 8.5.2   | EPLSB Radix Sort                      | 150          |

|    | 8.6  | Asymp   | ptotic number of cache and TLB misses | 154          |

|    | 8.7  | Experi  | imental results                       | 155          |

|    |      | 8.7.1   | Random inputs                         | 156          |

|    |      | 8.7.2   | Testing robustness                    | 158          |

|    |      | 8.7.3   | Sorted keys                           | 163          |

|    | 8.8  | Permu   | ting an array                         | 163          |

|    | 8.9  | Summ    | ary                                   | 164          |

| 9  | Opt  | imisin  | g predecessor searches in the IMM     | L66          |

|    | 9.1  | Data s  | structures                            | 168          |

|    | 9.2  | Experi  | imental results                       | 172          |

|    | 9.3  | Summ    | ary                                   | 175          |

| 10 | Lim  | itation | ns of the CMM and IMM                 | L <b>7</b> 6 |

|    | 10.1 | Simple  | e abstraction of reality              | 176          |

|    |      | 10.1.1  | Multi-level caches                    | 176          |

|    |      | 10.1.2  | Replacement policies                        | 7  |

|----|------|---------|---------------------------------------------|----|

|    |      | 10.1.3  | Pre-fetching data                           | 7  |

|    |      | 10.1.4  | Faster miss processing                      | 7  |

|    |      | 10.1.5  | Cache-coherency                             | '8 |

|    |      | 10.1.6  | Memory bandwidth                            | '8 |

|    |      | 10.1.7  | Physically mapped caches                    | 0  |

|    | 10.2 | Summa   | ary                                         | 2  |

| 11 | Con  | clusion | as and future work 18                       | 3  |

| A  | Sim  | ulation | results 19                                  | 5  |

| В  | Cacl | ne Arc  | hitecture 20                                | 3  |

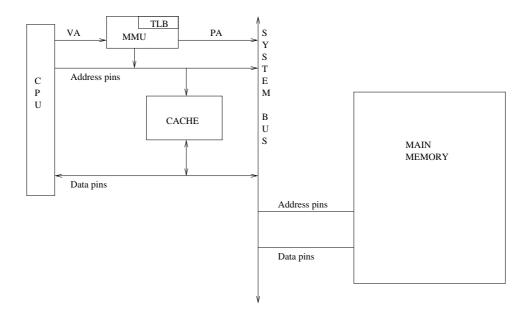

|    | B.1  | CPU a   | nd memory sub-system                        | 13 |

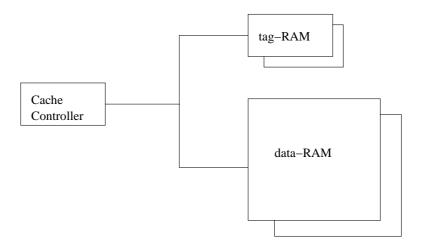

|    | B.2  | Cache   | organisation                                | 15 |

|    | B.3  | Blocke  | d memory                                    | 15 |

|    |      | B.3.1   | Block placement                             | 16 |

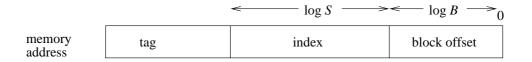

|    |      | B.3.2   | Block identification                        | 6  |

|    |      | B.3.3   | Block replacement                           | 17 |

|    | B.4  | Read a  | and write accesses to memory                | 18 |

|    |      | B.4.1   | Read access to a memory location            | 18 |

|    |      | B.4.2   | Write access to a memory location           | 18 |

|    | B.5  | Instruc | etion and data caches                       | .0 |

|    | B.6  | Non-ca  | cheable memory                              | .1 |

|    | B.7  | Read o  | only memory                                 | .1 |

|    | B.8  | Perform | nance measurement                           | .1 |

|    | B.9  | Improv  | ring performance                            | .1 |

|    |      | B.9.1   | Reducing cache misses                       | .2 |

|    |      | B.9.2   | Reducing miss penalties                     | .3 |

|    |      | B.9.3   | Reducing hit time                           | 6  |

|    | B.10 | Cache-  | coherency problem                           | .8 |

|    |      | B.10.1  | Coherency in single processor systems       | .8 |

|    |      | B.10.2  | Snooping using the cache's actual directory | .9 |

| Glossary |                                      | 224 |

|----------|--------------------------------------|-----|

| B.10.7   | Coherency in multi-processor systems | 222 |

| B.10.6   | Coherency in virtual caches          | 221 |

| B.10.5   | Snooping using dirty inclusion       | 221 |

| B.10.4   | Snooping using inclusion             | 220 |

| B.10.3   | Snooping using a dual directory      | 220 |

# List of Figures

| 1.1 | The typical memory hierarchy in computer systems before the mid 1980's.             | 16  |

|-----|-------------------------------------------------------------------------------------|-----|

| 1.2 | The typical memory hierarchy in recent computer systems                             | 16  |

| 1.3 | Flashsort1 vs Quicksort                                                             | 17  |

| 1.4 | Photograph of the Intel StrongArm chip                                              | 19  |

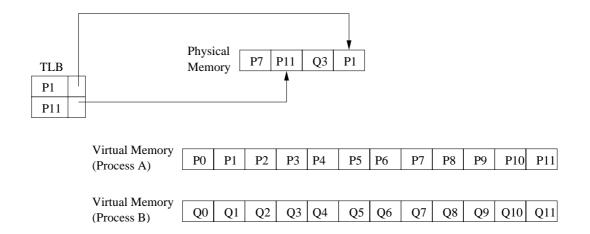

| 1.5 | Virtual memory, physical memory and TLB                                             | 21  |

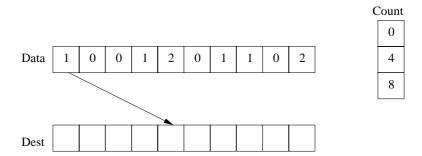

| 4.1 | Pseudo-code for count phase                                                         | 62  |

| 4.2 | Pseudo-code for out-of-place permute                                                | 62  |

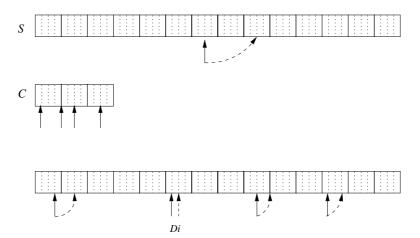

| 4.3 | Out-of-place permutation                                                            | 63  |

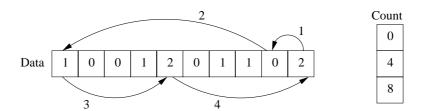

| 4.4 | Pseudo-code for in-place permute                                                    | 64  |

| 4.5 | In-place permutation                                                                | 64  |

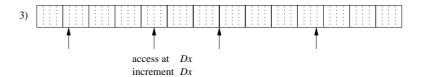

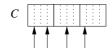

| 5.1 | Process "in-place"                                                                  | 73  |

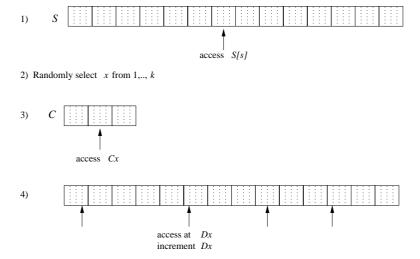

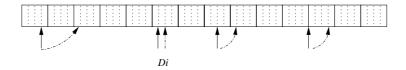

| 5.2 | Process "out-of-place"                                                              | 74  |

| 5.3 | Cache analysis of Process "in-place"                                                | 79  |

| 5.4 | Cache analysis of Process "out-of-place"                                            | 91  |

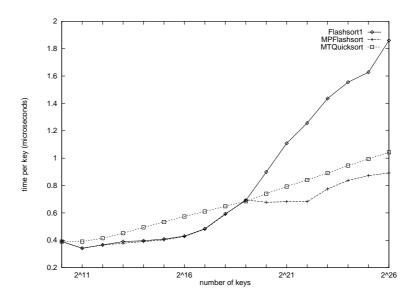

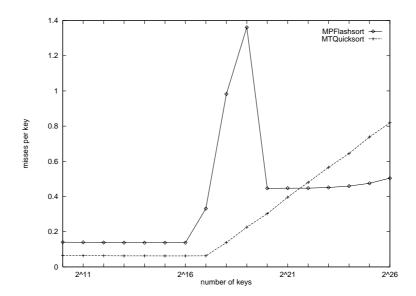

| 7.1 | Flashsort1, MPFlashsort and MTQuicksort                                             | 125 |

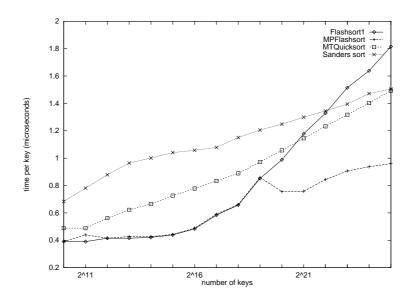

| 7.2 | Flashsort<br>1, MP<br>Flashsort, MT<br>Quicksort and Sanders Heapsort.<br>$8$ -byte |     |

|     | keys                                                                                | 127 |

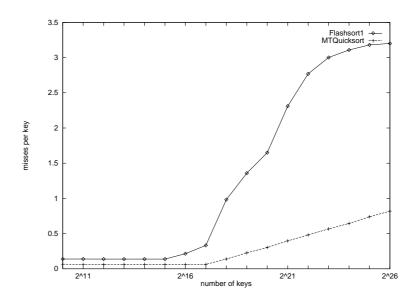

| 7.3 | L2 cache misses per key: Flashsort1 vs MTQuicksort                                  | 129 |

| 7.4 | L2 cache misses per key: MPFlashsort vs MTQuicksort                                 | 129 |

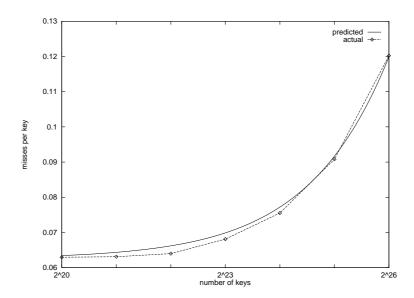

| 7.5 | Predicted vs simulated L2 cache misses per key: MPFlashsort                         | 130 |

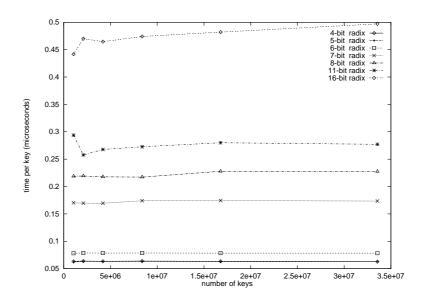

| 8.1 | Time per key for LSB: random integers                                               | 156 |

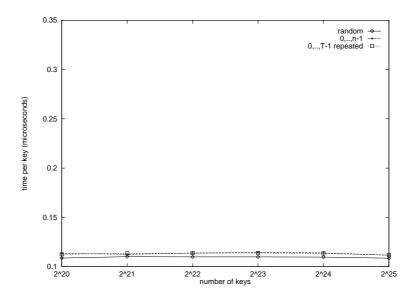

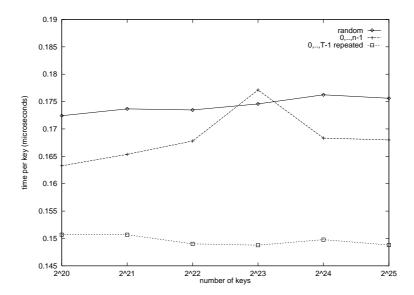

| 8.2 | Time per key for LSB5: random versus worst-case inputs                              | 159 |

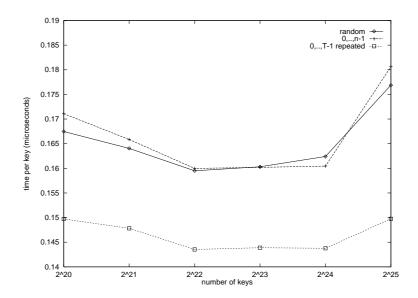

| 8.3 | Time per key for LSB6: random versus worst-case inputs        |

|-----|---------------------------------------------------------------|

| 8.4 | Time per key for EBT11: random versus worst-case inputs 160   |

| 8.5 | Time per key for PLSB11: random versus worst-case inputs 161  |

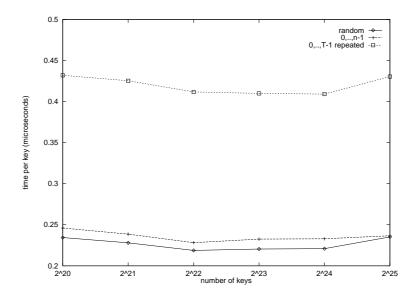

| 8.6 | Time per key for EPLSB10: random versus worst-case inputs 161 |

| 8.7 | Time per key for EPLSB11: random versus worst-case inputs 162 |

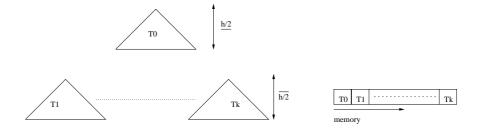

| 9.1 | Layout of Prokop's cache-oblivious search tree                |

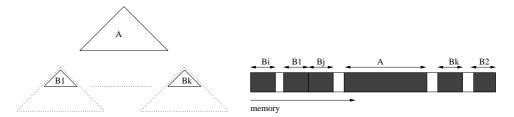

| 9.2 | External cache-oblivious search tree                          |

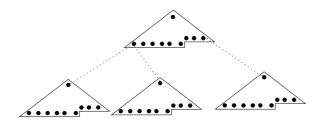

| 9.3 | A paged B-tree                                                |

| B.1 | CPU and memory sub-system                                     |

| B.2 | Cache components                                              |

| В.3 | Memory address                                                |

## List of Tables

| 7.1 | Flashsort1, MPFlashsort and MTQuicksort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 124 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.2 | Flashsort1, MPFlashsort, MTQuicksort and Sanders's Heapsort. 8-byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|     | keys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 126 |

| 7.3 | Flashsort1, MPFlashsort and MTQuicksort on an Intel Mobile Pentium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|     | III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 128 |

| 7.4 | MTQuicksort and Naive1 MSBRadix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 134 |

| 7.5 | MPFlashsort, MTQuicksort and MSBRadix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134 |

| 8.1 | LSB11 with random and worst-case inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 140 |

| 8.2 | LSB556, LSB6 and FLSB6 on random integers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 157 |

| 8.3 | LSB on random integers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 158 |

| 8.4 | EPLSB11,PLSB11,EBT11,LSB556,LSB6,LSB11,MTQuickandTMerged andMerged | 9   |

|     | on random integers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 158 |

| 8.5 | Pre-sorting and explicit block copy permutation of random integers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 164 |

| 9.1 | Query time per random key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 174 |

| 9.2 | Computation time per query                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 174 |

| A.1 | Accuray of approximate analyses: small classes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 196 |

| A.2 | Accuray of approximate analyses: large classes. Part 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 198 |

| A.3 | Accuray of approximate analyses: large classes. Part 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 199 |

| A.4 | $n=2^{20}$ : more than 5% between predicted and actual $\nu$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 199 |

| A.5 | $n=2^{22}$ : more than 5% between predicted and actual $\nu$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200 |

| A.6 | $n=2^{24}$ : more than 5% between predicted and actual $\nu.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 201 |

| ۸ 7 | A source or of A bounistic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 202 |

## Chapter 1

### Introduction

Application programs, dealing with increasingly large data sets, require a large memory to hold data and the results of computation. In many cases they also require the computation to be done as fast as possible. Increases in CPU speeds go some way towards meeting the need for speed. However the time to access data is usually a significant proportion of the overall computation time. The designers of computer systems need to meet the demand for a large storage capacity which can be accessed at high speeds, but at the same time they must minimise overall system costs. The cost of memory varies with the technology used. A tradeoff is made, where computers instead use a hierarchy of memories, where the size of each memory varies inversely with its speed and unit storage cost. The size of the memory also varies with its distance from the CPU. Such that, memories which are increasingly closer to the CPU are smaller, faster and more expensive. The hierarchy of memories exploits the fact that many computer programs have good *locality of reference*, where nearby memory locations are, often repeatedly, accessed around the same time. The faster, smaller, memories are used to keep subsets of data likely to be referenced in the near future. This allows data to be supplied at high speed to the CPU, as most memory accesses take place at the same speed as the faster memories, only when the subsets of data held in the faster memories do not contain the required data are the slower memories accessed.

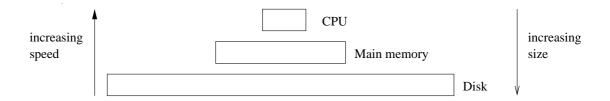

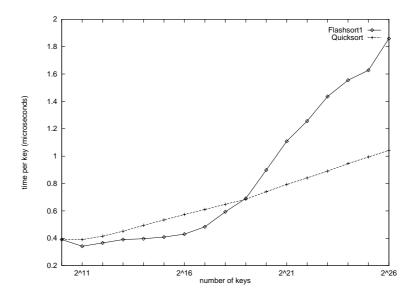

Until the mid 1980s most CPUs were only a few times faster than main memory and the memory hierarchy in most computers consisted of the CPU registers, main memory and disk, see Figure 1.1. If all the data used by a program fitted in main memory then, until the mid 1980s using the random access machine (RAM) model of

Figure 1.1: The typical memory hierarchy in computer systems before the mid 1980's.

Figure 1.2: The typical memory hierarchy in recent computer systems.

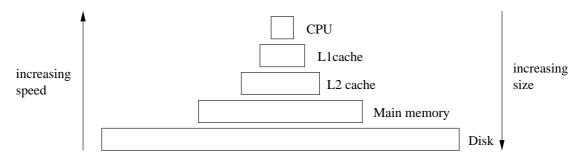

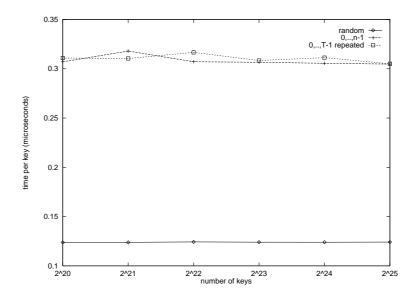

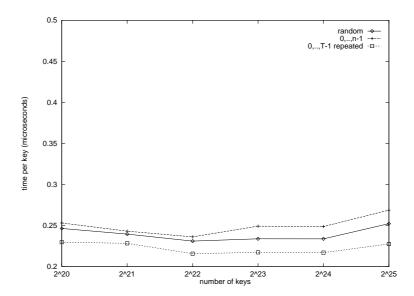

computation [9] gave a fairly good prediction of performance. In the RAM model it is assumed that accessing a location in memory costs the same as a built-in arithmetic operation, such as adding two word-sized operands. Unfortunately this is no longer true. Consider the following example, which compares the performance of two sorting algorithms on a more recent computer system. Figure 1.3 shows the time per key to sort n uniformly-random single-precision floating-point numbers using a distribution sorting algorithm, Flashsort1, with an expected O(n) running time and using Quicksort with an expected  $\Theta(n \log n)$  running time. Both the algorithms have small constant factors. We consider quite large values of n, up to 67M. The asymptotic analysis of the running times tell us that, for sufficiently large n, as n grows the time per key for Flashort1 should remain constant and for Quicksort it should grow proportional to  $\log n$ . This suggests that for sufficiently large n, once Flashsort1 becomes faster than Quicksort, it should remain faster as n grows. However this is not true for n up to 67M. We see that for small n Flashsort1 is fast but for large n it is considerably slower than Quicksort. The algorithms are 'in-place', in that they use little additional memory, Flashsort1 uses  $\approx 4.4n$  bytes and Quicksort uses  $\approx 4n$  bytes. The running times are reported on a computer with 1GB of main memory, so there is almost no possibility of swapping code or data to disk during these experiments. In order to understand these running times we have to consider more recent developments in the memory hierarchy

Figure 1.3: Time per key to sort single-precision floating-point keys using Flashsort1 and Quicksort on a Sun UltraSparc-II. For  $n = 2^i, i = 10, ..., 26$ . Note that the x-axis is on a log scale.

of modern computer systems.

Over the last 20 years or so, CPU clock rates have grown explosively, and CPUs with clock rates exceeding 2GHz are now available in the mass market. Unfortunately, the speed of main memory has not increased as rapidly: today's main memory typically has a latency of about 60ns. This implies that the cost of accessing main memory can be 120 times greater than the cost of performing an operation on data which are in the CPU's registers. Since the driving force behind CPU technology is speed and the primary driving force behind memory technology is storage capacity, this trend is likely to continue. In order to bridge this ever increasing performance gap, since the mid 1980s computer systems intended for the mass market have used one or more levels of cache memory between the CPU registers and main memory, see Figure 1.2.

Due to costs, caches are much smaller than main memory. In the example in Figure 1.3 the computer has a 512KB cache which is about 10-15 times faster than main memory. Since each key is four bytes, in both the algorithms, for  $n \leq 2^{16}$  all the keys and additional data fit in cache. We see that for  $n \leq 2^{16}$ , the time per key grows more slowly for Flashsort1 than for Quicksort, however when the problem no longer fits in cache we see that the rate of increase in the time per key is much more for Flashsort1. This suggests that the performance of Flashsort1 is affected quite dramatically by the

cache. It is clear that the RAM model may fail spectacularly to predict performance on modern computers. We need a model that considers both computation and memory access costs.

It is only fairly recently that improving cache usage has been identified as an important issue. For example, for many years the database community has been aware of the importance of improving algorithm and data structure design in order to reduce disk accesses, however it has only fairly recently been reported that in many standard database applications the bottleneck is main memory computation, caused by poor cache usage [10].

Movement of data between the disk and main memory is under software control, this may be through system or application software. This approach gives more flexibility than with hardware control but with relatively small overheads. The cost of an access to disk may be equivalent to a million CPU clock cycles (referred to as cycles in the future) and the cost of software control is amortised in the overall costs of the access. In contrast, movement of data between the main memory and cache(s) is always under hardware control. There are several reasons for this:

- Controlling the efficient movement of data between multiple levels of memory is a complex task, instead programmers like to develop software on a relatively simple model of the underlying machine architecture. Most programs are developed on the von Neumann architecture, which is modelled by the RAM model. This architecture assumes a single, sequentially addressed, memory. The programmer assumes that the operating system and compiler are responsible for the messy details of providing this virtualisation.

- By the time caches became widespread, a large number of applications had already been developed assuming the von Neumann architecture. If caches required programmer control then these applications would have to be rewritten in order to take advantage of the cache.

- The constant factors between main memory and CPU speeds are much less than

those between disk and CPU speeds, so it is much more important to keep the

overheads of using a cache low. Hardware control is much faster than any software

control would be.

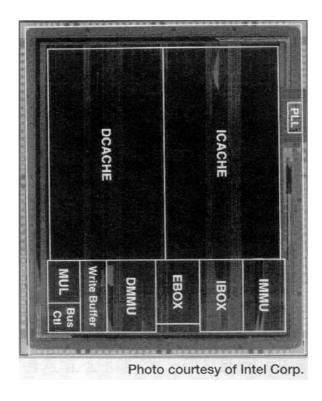

Figure 1.4: Photograph of the Intel StrongArm chip.

A large number of algorithmic techniques have been developed to improve locality in main memory accesses and so reduce accesses to disk. It seems reasonable to exploit these techniques to improve locality in caches and reduce accesses to main memory. However, since placement of data in a cache is hardware rather than software controlled, these techniques can not always be applied directly.

Caches not only improve speed of computation, but can also help with reducing power consumption, an important issue for handheld computing devices. The importance of the cache in the design of modern computer systems is demonstrated by the design of the Intel StrongArm chip. Figure 1.4 shows a photograph of this chip. This unit is used in many handheld computing devices such as PDA, and we see that a large proportion of the chip is occupied by two 16KB caches, the DCACHE and the ICACHE. Off-chip accesses to main memory consume more power than accesses to on-chip locations, and the large caches are used to improve locality and reduce off-chip accesses.

#### 1.1 Internal memory hierarchy

We now give a brief overview of the memory hierarchy between the CPU and main memory.

#### 1.1.1 Caches

A cache is a fast memory which holds the contents of some main memory locations. If the CPU requests the contents of a main memory location, and the contents of that location is held in some level of cache, the CPU's request is answered by the cache itself (a cache hit); otherwise it is answered by consulting the main memory (a cache miss). A cache hit has small or no cost (penalty), 1-3 CPU cycles is fairly typical, but a cache miss requires a main memory access, and is therefore very expensive. To amortise the cost of a main memory access in case of a cache miss, an entire block of consecutive main memory locations which contains the location accessed is brought into cache on a miss. Programs which have good spatial locality, where an access to a memory location is followed by an access to a nearby memory location, benefit from the fact that data are transferred from main memory to cache in blocks. While programs which have good temporal locality, where a memory location once accessed is soon accessed again, benefit from the fact that caches hold several blocks of data. Such programs make fewer cache misses and consequently run faster.

#### 1.1.2 TLB

There is an important optimisation which can contribute as much or more to performance as minimising cache misses, namely minimising misses in the translation-look-aside buffer (TLB). Some papers from the early and mid 90's (see e.g. [5, 66]) have noted the importance of minimising TLB misses when implementing algorithms, but there has been no systematic study of this optimisation, even though TLB misses are often at least as expensive as cache misses. A major contribution of this thesis is to study TLB misses systematically.

The TLB is used to support *virtual memory* in multi-processing operating systems [45]. Virtual memory means that the memory addresses accessed by a process refer to its own unique logical address space. This logical address space contains as

Figure 1.5: Virtual memory for processes A and B, each with 12 pages. Physical memory with 4 pages. TLB holds virtual (logical) page to physical page translations for 2 pages.